7 dynamic vccp monitoring using vid, 8 vref output, 9 prochot background information – Rainbow Electronics LM93 User Manual

Page 15: 7 dynamic vccp monitoring using vid 12.8 v, Output, 0 functional description

12.0 Functional Description

(Continued)

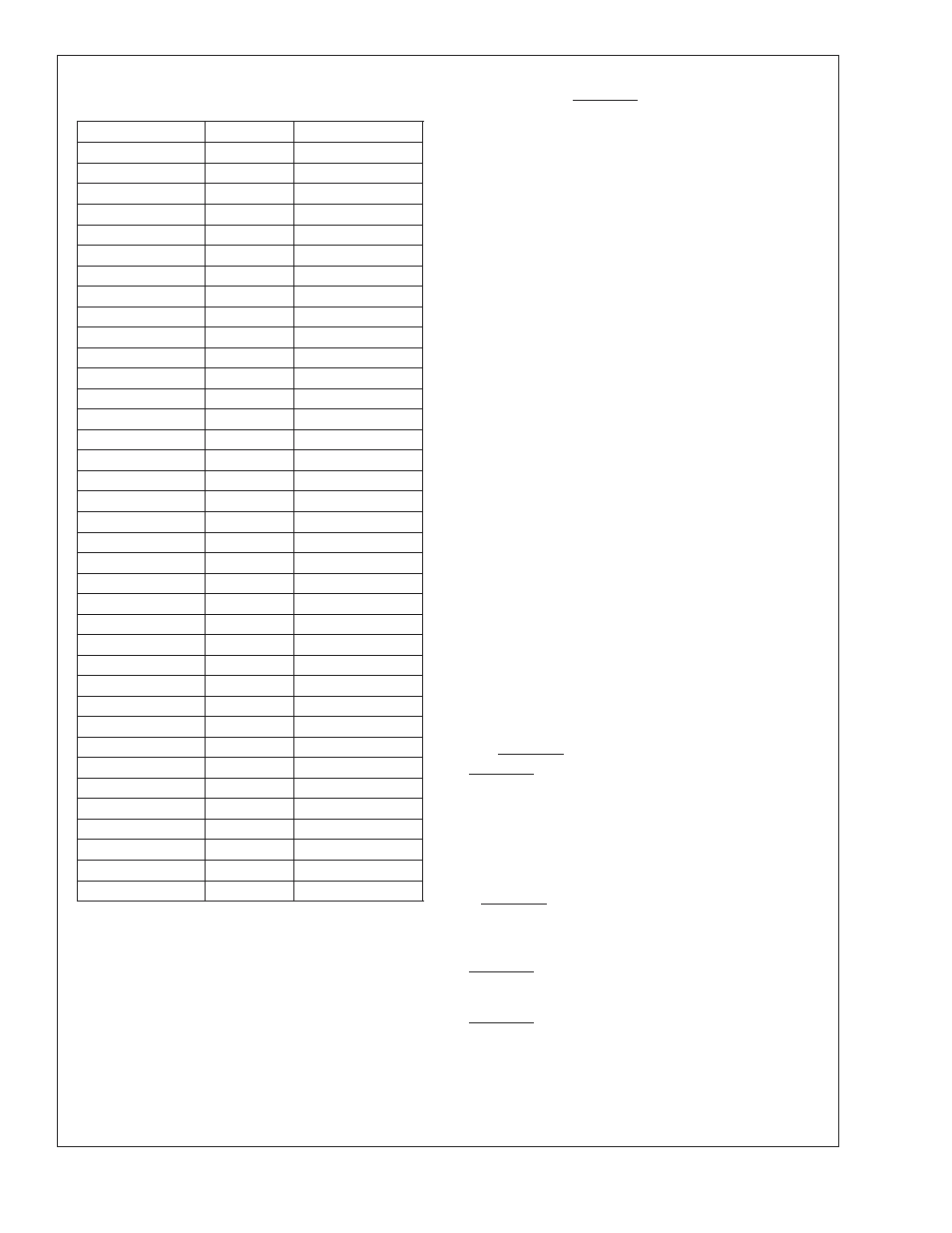

Value Register

V

IN

%

∆ from −12V

77

-11.6758

2.7014

78

-11.6511

2.9072

79

-11.6264

3.1130

80

-11.6018

3.3188

81

-11.5771

3.5245

82

-11.5524

3.7303

83

-11.5277

3.9361

84

-11.5030

4.1418

85

-11.4783

4.3476

86

-11.4536

4.5534

87

-11.4289

4.7591

88

-11.4042

4.9649

89

-11.3795

5.1707

90

-11.3548

5.3765

91

-11.3301

5.5822

92

-11.3054

5.7880

93

-11.2807

5.9938

94

-11.2561

6.1995

95

-11.2314

6.4053

96

-11.2067

6.6111

97

-11.1820

6.8168

98

-11.1573

7.0226

99

-11.1326

7.2284

100

-11.1079

7.4342

101

-11.0832

7.6399

102

-11.0585

7.8457

103

-11.0338

8.0515

104

-11.0091

8.2572

105

-10.9844

8.4630

106

-10.9597

8.6688

107

-10.9351

8.8745

108

-10.9104

9.0803

109

-10.8857

9.2861

110

-10.8610

9.4919

111

-10.8363

9.6976

112

-10.8116

9.9034

113

-10.7869

10.1092

12.7 DYNAMIC Vccp MONITORING USING VID

The AD_IN7 (CPU1 Vccp) and AD_IN8 (CPU2 Vccp) inputs

are dynamically monitored using the P1_VIDx and P2_VIDx

inputs to determine the limits. The dynamic comparisons

operate independently of the static comparisons which use

the statically programmed limits.

According to the VRM/VRD 10 specification when a VID

signal is ramping to a new value, it steps by one LSB at a

time, and one step occurs every 5 µs. In worse case, up to

20 steps may occur at once over 100 µs. The Vccp voltage

from the VRD has to settle to the new value within 50 µs of

the last VID change. The LM93 expects that the VID

changes will not occur more frequently than every 5 µs.

The VID signal can be changed by the processor under

program control, by internal thermal events or by external

control, like force PROCHOT.

The reference voltages selected by each value of the 6 bit

VID can be found in the VRM/VRD 10 spec. Transient VID

values caused by line-to-line skew are ignored by the LM93.

See the VRM/VRD 10 spec for the worst case line-to-line

skew.

The LM93 averages the VID values over a sampling window

to determine the average voltage that the VID input was

indicating during the sampling window. At the completion of a

voltage conversion cycle the LM93 performs limit compari-

sons based on average VID values and not instantaneous

values. The upper limit is determined by adding the upper

limit offset to the average voltage indicated by VID. The

lower limit is determined by subtracting the lower limit offset

from average voltage indicated by VID. If the AD_IN7 (or

AD_IN8) voltage falls outside the upper and lower limits, an

error event is generated. Dynamic and static comparisons

are performed once every 100 ms. The averaging time inter-

val is 1.5 ms.

If at any time during the Vccp sampling window, the VID

code indicates that the VRD should turn off its output, the

dynamic Vccp checking is disabled for that sample.

The comparison accuracy is

±

25 mV, therefore the compari-

son limits must be set to include this error. Since the Vccp

voltage may be in the process of settling to a new value (due

to a VID change), this settling should be taken into account

when setting the upper and lower limit offsets.

The LM93 has a limitation on the upper limit voltage for

dynamic Vccp checking. The upper limit cannot exceed

1.5875V. If the sum of the voltage indicated by VID and the

upper offset voltage exceed 1.5875, the upper limit checking

is disabled.

12.8 V

REF

OUTPUT

V

REF

is a fixed voltage to be used by an external VRD or as

a voltage reference input for the BMC A/D inputs. V

REF

is

2.5V

±

1%. There is internal current limit protection for the

V

REF

output in case it gets shorted to supply or ground

accidentally.

12.9 PROCHOT BACKGROUND INFORMATION

PROCHOT is an output from a processor that indicates that

the processor has reached a predetermined temperature trip

point. At this trip point the processor can be programmed to

lower its internal operating frequency and/or lower its supply

voltage by changing the value of the 6 bit VID that it supplies

to the VRD. The final VID setting and the rate at which it

transitions to the new VID is programmable within the pro-

cessor.

If PROCHOT is 100% throttled, it does not mean that the

CPU is not executing, but it may mean that the CPU is about

to encounter a thermal trip if the processor temperature

continues to rise.

PROCHOT is also an input to some processors so that an

external controller can force a thermal throttle based on

external events.

PROCHOT is no longer asserted by the processor when the

temperature drops below the predefined thermal trip point.

Oscillation around the trip point is avoided by the processor

by requiring that the temperature be above/below the trip

point for a predetermined period of time. A counter inside the

processor is used to track this time and it has to be incre-

LM93

www.national.com

15