5 smbus fixed address block reads, 0 smbus interface – Rainbow Electronics LM93 User Manual

Page 24

14.0 SMBus Interface

(Continued)

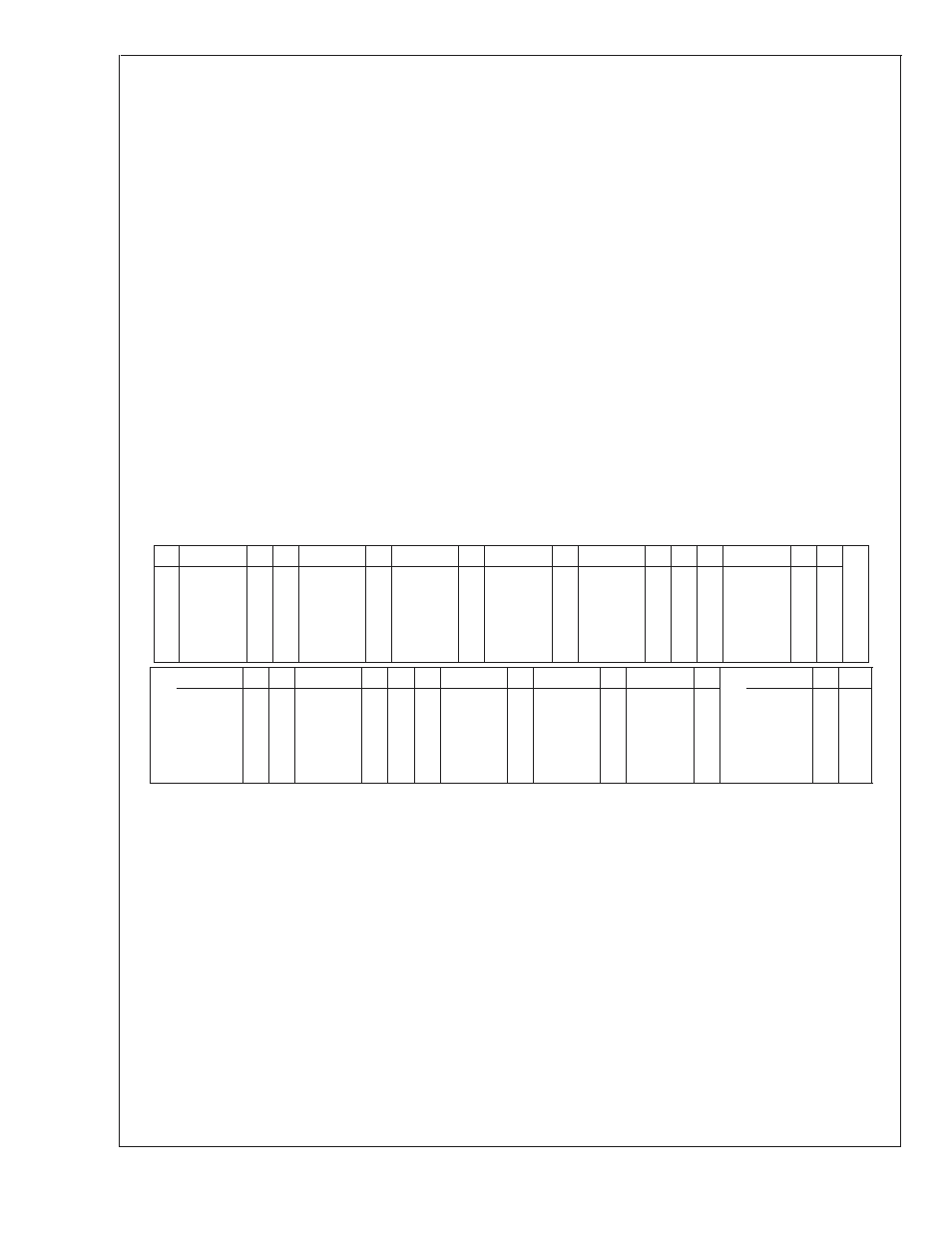

14.5.4.4 Simulated SMBus Block-Write Block-Read Process Call

Alternatively, if the master cannot support an SMBus Block-Write Block-Read process call, it can be emulated by two transactions

(a block write followed by a block read). This should only be done in a single master system, since in a dual master system

collisions can occur that corrupt the data and transaction. Below is the sequence of events for these transactions:

1.

The master issues a START to start this transaction.

2.

The master sends the 7-bit slave address followed by a write bit (low).

3.

The slave asserts the ACK.

4.

The master sends the Block Read command code (F1h) and the slave asserts the ACK.

5.

The master sends the Byte Count (2h) for this transaction and the slave asserts the ACK.

6.

The master sends the Start Register Address and the slave asserts the ACK.

7.

The master sends the Byte Count (1-20h) for the Block-Read Process Call and the slave asserts the ACK.

8.

The master sends a STOP to end this transaction.

9.

The master sends a START to start this transaction.

10. The master sends the 7-bit slave address followed by a write bit (low) and the slave asserts the ACK.

11. The master sends the Block Read Command code (F1h) and the slave asserts the ACK.

12. The master sends a repeat START.

13. The master sends the 7-bit slave address followed by a read bit (high) and the slave asserts the ACK.

14. The master receives Byte Count (this matches the size sent by the master in step 7) and asserts the ACK.

15. The master receives Data Byte 1 and asserts the ACK.

16. The master receives Data Byte 2 and asserts the ACK.

17. The master receives N-3 data bytes, and asserts ACK for each one.

18. The master receives the last data byte and asserts a NACK.

19. The master issues a STOP to end this transaction.

1

2

3

4

5

6

7

8

9

10

S

Slave

Address

W

A

Block

Read

Command

Code

(F1h)

A

Byte

Count

(2h)

A

Start

Register

Address

A

Byte

Count

(1–20h)

(N)

A

P

S

Slave

Address

W

A

A

11

12 13

14

15

16

17

16

A

Block

Read

Command

Code

(F1h)

A

S

Slave

Address

R

A

Byte

Count

(1–20h)

(N)

A

Data

Byte 1

A

Data

Byte 2

A

A

Data

Byte N

/A

P

Special Notes:

1.

Steps 9 through 19 can be repeated to read another block of data. The address auto-increments such that the next block

starts where the last block left off. The size returned by the LM93 is the same each time.

2.

The LM93 returns 00h when address locations outside of normal address space are read.

3.

Block reads do not wrap around from address FFh to 00h

4.

If the master acknowledges more bytes that it requested, the LM93 continues to supply data until the master does not

acknowledge a byte.

5.

If the master does not acknowledges a byte to prematurely abort a block read, the LM93 gets off the bus to allow the master

to issue a STOP signal.

6.

After a block read is finished, the base address of the LM93 is updated to point to the byte just beyond the last byte read.

14.5.4.5 SMBus Fixed Address Block Reads

Block reads can be performed from pre-defined addresses. A special command code has been reserved for each pre-defined

address. See the Section 14.5.2 Block Command Code Summary for more details on the command codes. Below is the

sequence of events that occur for this type of block read:

1.

The master sends a START to start this transaction.

2.

The master sends the 7-bit slave address followed by a write bit (low).

3.

The slave asserts an ACK.

4.

The master sends a Fixed Block Command Code (F2h-FDh) and the slave asserts an ACK.

LM93

www.national.com

24