6 register 45hb_p2_prochot error status, 7 register 46hb_gpi error status, 6 register 45h – Rainbow Electronics LM93 User Manual

Page 44: B_p2_prochot error status, 7 register 46h, B_gpi error status, 0 registers

16.0 Registers

(Continued)

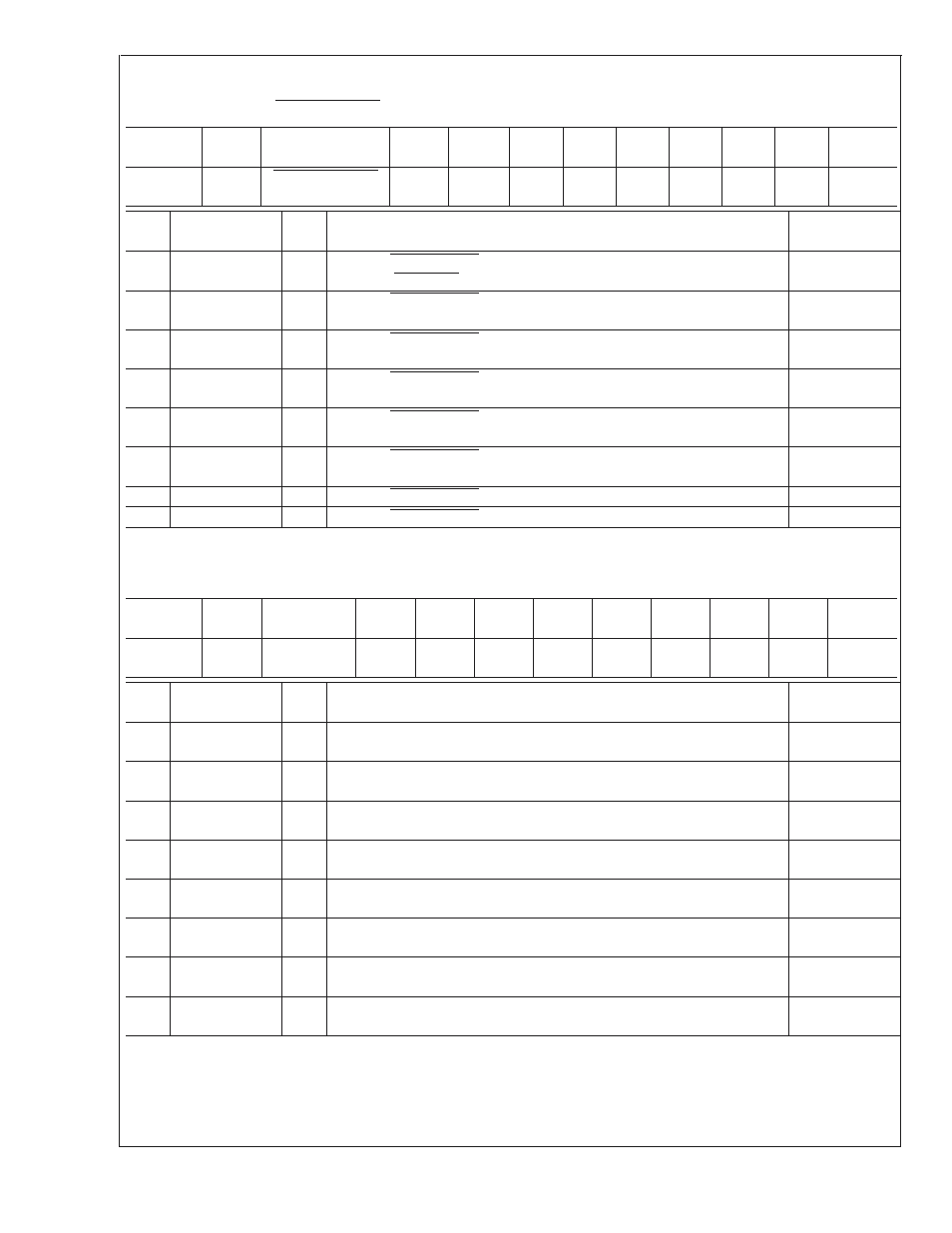

16.4.6 Register 45h

B_P2_PROCHOT Error Status

Register

Address

Read/

Write

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Default

Value

45h

RWC

B_P2_PROCHOT

Error Status

PH2

_ERR

TMAX

T100

T75

T50

T25

T12

T0

00h

Bit

Name

R/W

Description

Sleep

Masking

0

T0

RWC Set when P2_PROCHOT has had a throttled event. This bit is set for any

amount of PROCHOT throttling

>

0%.

S3, S4/5

1

T12

RWC Set when P2_PROCHOT has throttled greater than or equal to 0.0% but less

than 12.5%.

S3, S4/5

2

T25

RWC Set when P2_PROCHOT has throttled greater than or equal to 12.5% but

less than 25%.

S3, S4/5

3

T50

RWC Set when P2_PROCHOT has throttled greater than or equal to 25% but less

than 50%.

S3, S4/5

4

T75

RWC Set when P2_PROCHOT has throttled greater than or equal to 50% but less

than 75%.

S3, S4/5

5

T100

RWC Set when P2_PROCHOT has throttled greater than or equal to 75% but less

than 100%.

S3, S4/5

6

TMAX

RWC Set when P2_PROCHOT has throttled 100%.

S3, S4/5

7

PH2_ERR

RWC Set when P2_PROCHOT has throttled more than the user limit.

S3, S4/5

The PH2_ERR bit is the only bit in this register that will set BMC_ ERR in the LM93 Status/Control register.

16.4.7 Register 46h

B_GPI Error Status

Register

Address

Read/

Write

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Default

Value

46h

RWC

B_GPI

Error Status

GPI7

_ERR

GPI6

_ERR

GPI5

_ERR

GPI4

_ERR

GPI3

_ERR

GPI2

_ERR

GPI1

_ERR

GPI0

_ERR

00h

Bit

Name

R/W

Description

Sleep

Masking

0

GPI0_ERR

RWC This bit is set whenever GPIO0 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

1

GPI1_ERR

RWC This bit is set whenever GPIO1 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

2

GPI2_ERR

RWC This bit is set whenever GPIO2 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

3

GPI3_ERR

RWC This bit is set whenever GPIO3 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

4

GPI4_ERR

RWC This bit is set whenever GPIO4 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

5

GPI5_ERR

RWC This bit is set whenever GPIO5 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

6

GPI6_ERR

RWC This bit is set whenever GPIO6 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

7

GPI7_ERR

RWC This bit is set whenever GPIO7 is driven low (unless masked via the GPI

Error Mask register).

S1*, S3*, S4/5*

LM93

www.national.com

44