24 register e2hlm93 status control, 24 register e2h, Lm93 status control – Rainbow Electronics LM93 User Manual

Page 78: 0 registers

16.0 Registers

(Continued)

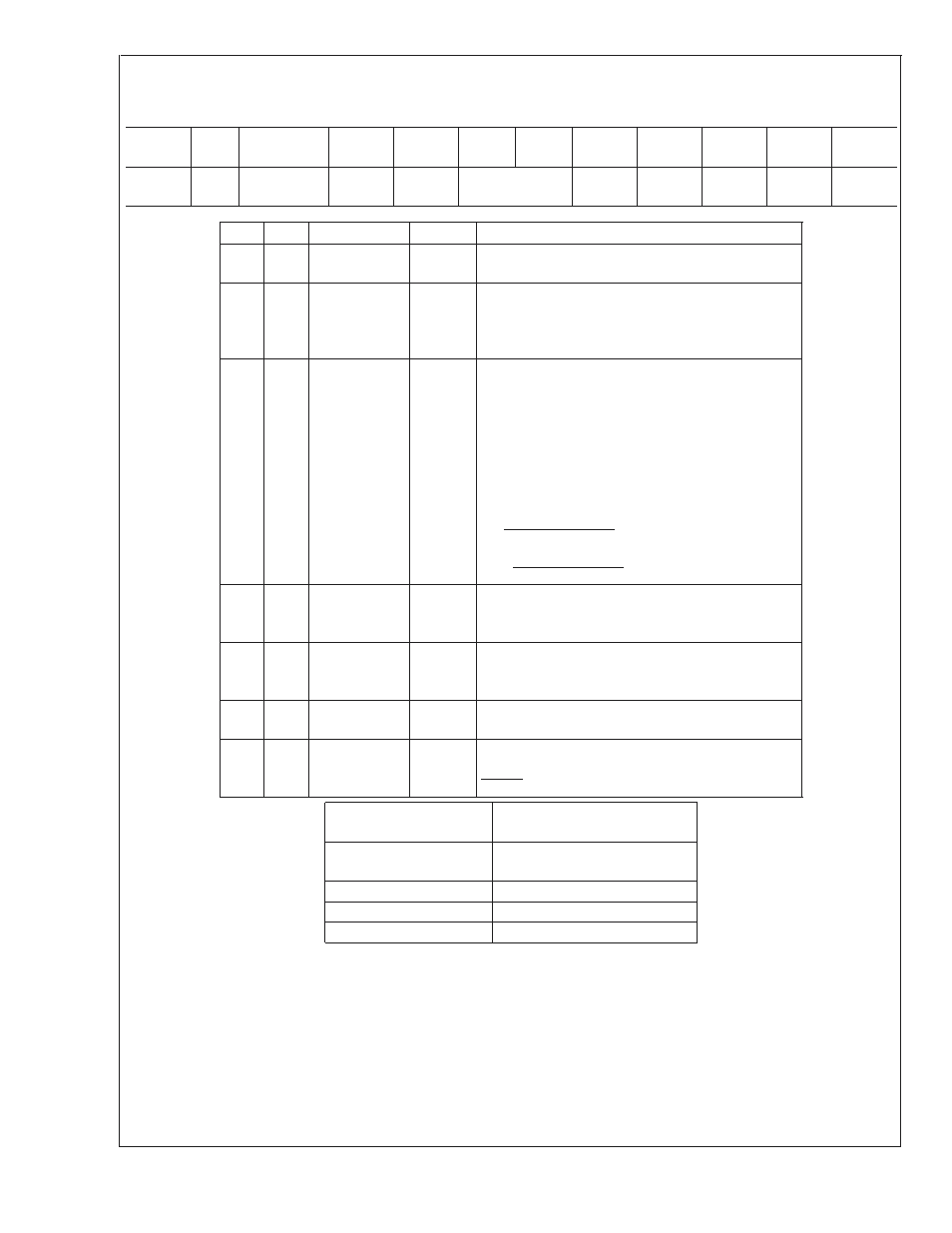

16.8.24 Register E2h

LM93 Status Control

Register

Address

Read/

Write

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Default

Value

E2h

R/W

LM93 Status/

Control

BMC

_ERR

HOST

_ERR

TACH_EDGE

GPI5_AM GPI4_AM

ASF

OVRID

00h

Lock

Bit

Name

R/W

Description

0

OVRID

R/W

If this bit is set, all PWM outputs go to 100% duty

cycle.

X

1

ASF

R/W

If this bit is set, BMC error registers support ASF, i.e.

reset on read. When not in ASF mode, a write “1” is

required to clear the bits in the BMC error status

registers.

2

GPI4_AM

R/W

GPI4 Auto Mask Enable

If this bit is set, an error event on GPI4 causes all

other error events to be masked.

The BMC Error Status registers do not reflect any

new error events until the GPI4_ERR bit is cleared in

the B_GPI Error Status register. The HOST Error

Status registers do not reflect any new error events

until the GPI4_ERR bit is cleared in the H_GPI Error

Status register.

If a CPU_THERMTRIP signal is connected to GPIO4,

this ensures that unwanted error events do not fire

once CPU_THERMTRIP is asserted.

3

GP15_AM

R/W

GPI5 Auto Mask Enable

This bit works exactly the same as GPI4_AM, but

applies to GPI5.

5:4

TACH_EDGE

R/W

This field determines what type of edges are used for

measuring fan tach pulses. This effects all four

tachometer inputs.

6

HOST_ERR

R

This bit gets set if any error bit is set in any of the

Host Error Status registers (H_).

7

BMC_ERR

R

This bit gets set if any error bit is set in any of the

BMC Error Status registers (B_). When this bit is set,

ALERT are asserted if enabled.

TACH_EDGE

Edge Type Used for

Tachometer Measurements

0h

Either rising or falling edges may

be used.

1h

Rising edges only

2h

Falling edges only

3h

Reserved

LM93

www.national.com

78