Table 02h register descriptions, Ds1876 sfp controller with dual ldd interface – Rainbow Electronics DS1876 User Manual

Page 44

44 _____________________________________________________________________________________

DS1876

SFP Controller with Dual LDD Interface

Table 01h, Register FDh–FFh: RESERVED

Table 02h Register Descriptions

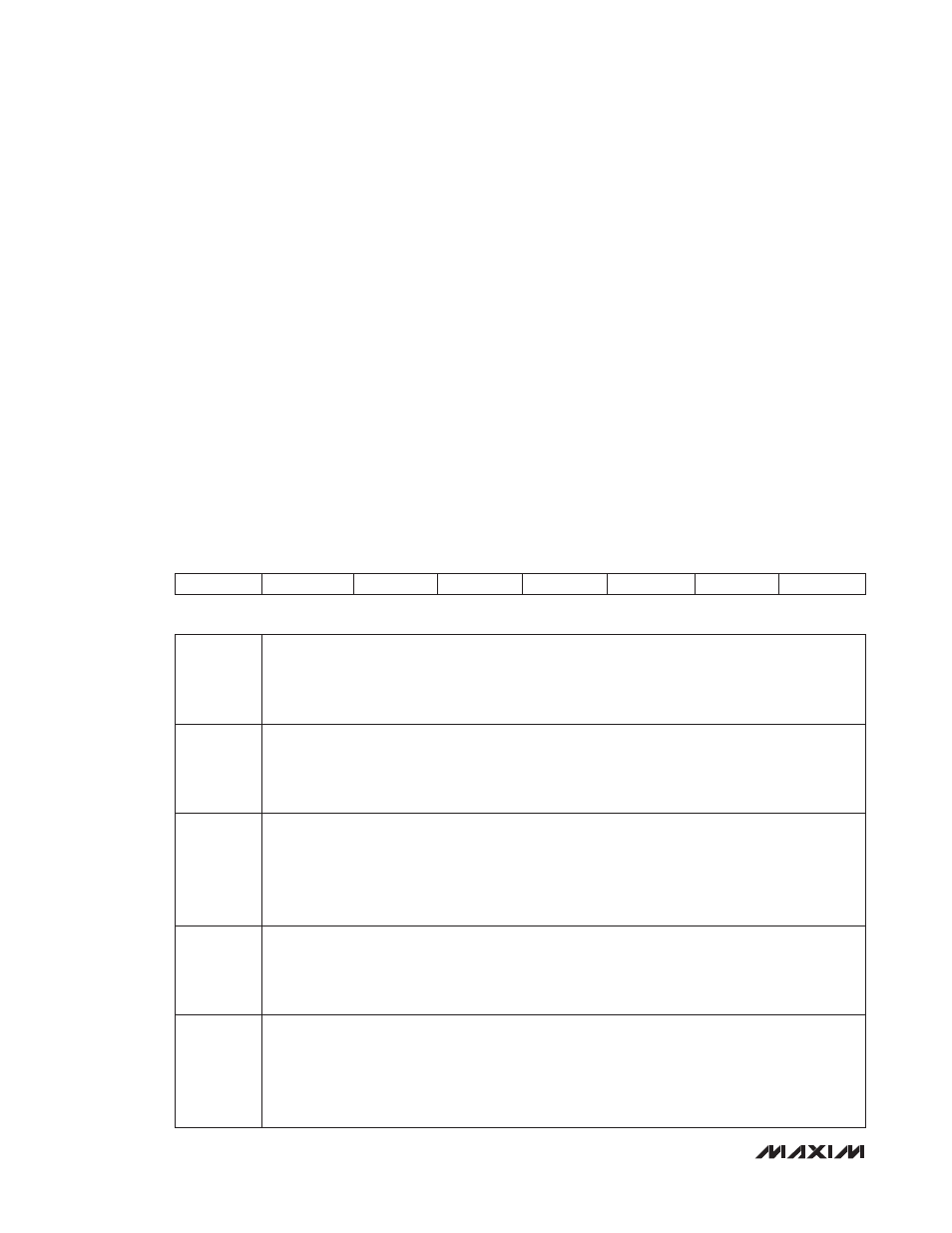

Table 02h, Register 80h: MODE

POWER-ON VALUE

READ ACCESS

N/A

WRITE ACCESS

N/A

A2h AND B2h MEMORY

N/A

MEMORY TYPE

N/A

These registers are reserved.

POWER-ON VALUE

7Fh

READ ACCESS

PW2 or (PW1 and RWTBL2) or (PW1 and RTBL2)

WRITE ACCESS

PW2 or (PW1 and RWTBL2)

A2h AND B2h MEMORY

Common A2h and B2h memory location

MEMORY TYPE

Volatile

80h

SEEB

MOD2EN

QT2EN

APC2EN

AEN

MOD1EN

QT1EN

APC1EN

BIT 7

BIT 0

BIT 7

SEEB:

0 = (default) Enables EEPROM writes to SEE bytes.

1 = Disables EEPROM writes to SEE bytes during configuration, so that the configuration of the

part is not delayed by the EE cycle time. Once the values are known, write this bit to a 0 and write

the SEE locations again for data to be written to the EEPROM.

BIT 6

MOD2EN:

0 = MOD2 DAC is writable by the user and the LUT recalls are disabled. This allows the user to

interactively test their modules by writing the values for MOD2. The output is updated with the new

value at the end of the write cycle. The I

2

C STOP condition is the end of the write cycle.

1 = (default) Enables automatic control of the LUT for MOD2 DAC.

BIT 5

QT2EN:

0 = QTs (HBIAS, TXP HI, TXP LO) for transmitter 2 are writable by the user and the LUT recalls are

disabled. This allows the user to interactively test their modules by writing to the QT thresholds.

The thresholds are updated with the new values at the end of the write cycle. The I

2

C STOP

condition is the end of the write cycle.

1 = (default) Enables automatic control of the LUT QTs for transmitter 2.

BIT 4

APC2EN:

0 = APC2 DAC is writable by the user and the LUT recalls are disabled. This allows the user to

interactively test their modules by writing the values for APC2. The output is updated with the new

value at the end of the write cycle. The I

2

C STOP condition is the end of the write cycle.

1 = (default) Enables automatic control of the LUT for APC2 DAC.

BIT 3

AEN:

0 = The temperature-calculated index value TINDEX is writable by the user and the updates

of calculated indexes are disabled. This allows the user to interactively test their modules by

controlling the indexing for the LUTs. The recalled values from the LUTs appear in the DAC

registers after the next completion of a temperature conversion.

1 = (default) The temperature-calculated index value TINDEX is used to control the LUTs.