Ds1876 sfp controller with dual ldd interface – Rainbow Electronics DS1876 User Manual

Page 17

______________________________________________________________________________________ 17

DS1876

SFP Controller with Dual LDD Interface

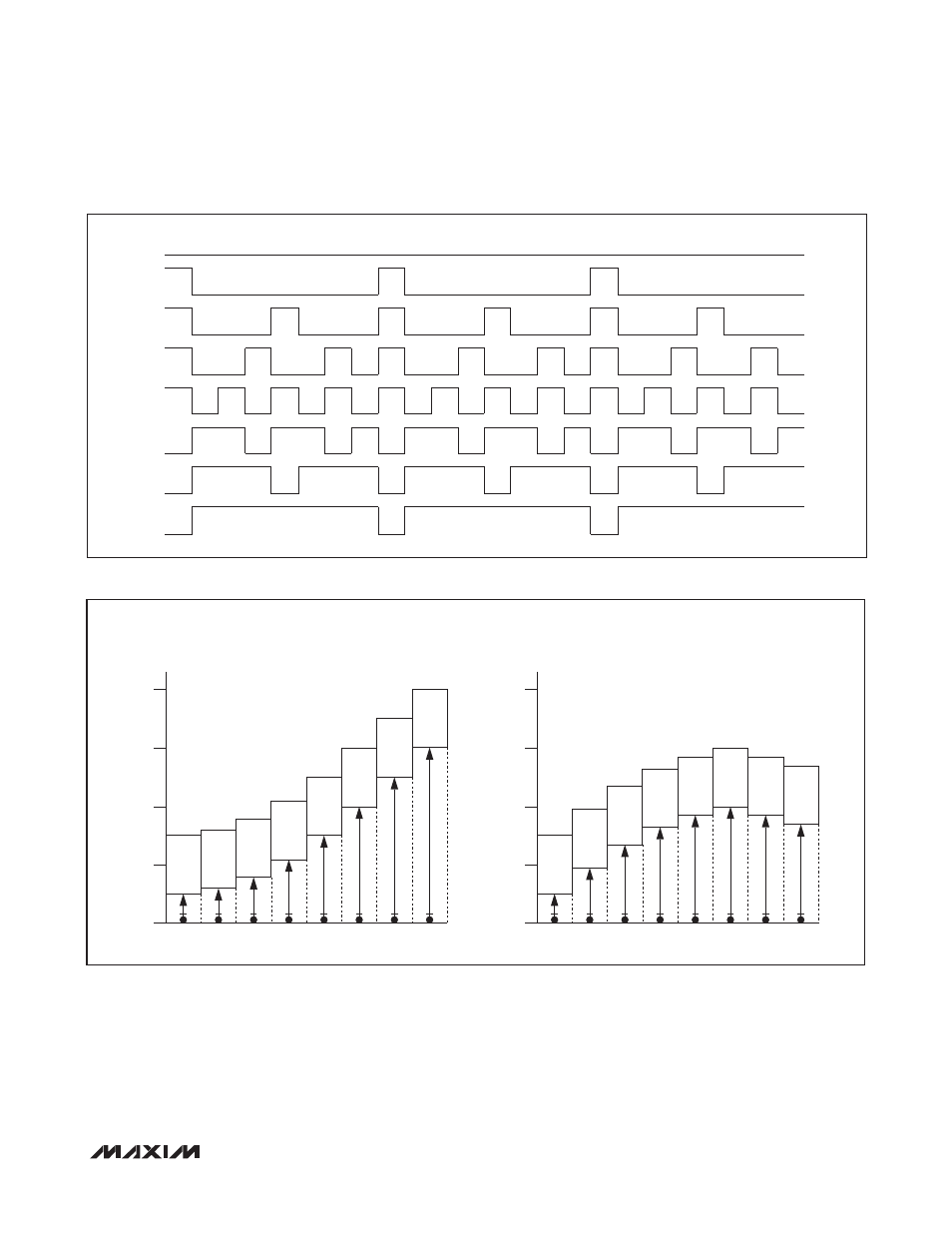

Figure 7. 3-Bit (8-Position) Delta-Sigma Example

Figure 8. DAC OFFSET LUTs

When temperature controlled, the DACs are updated

after each temperature conversion.

The reference input, REFIN, is the supply voltage for the

output buffer of all four DACs. The voltage connected to

REFIN and its decoupling must be able to support the

edge rate requirements of the delta-sigma outputs. In

a typical application, a 0.1FF capacitor should be con-

nected between REFIN and ground.

O

1

2

3

4

5

6

7

DAC OFFSET LUTs (04h/06h)[A2h/B2h]

EIGHT REGISTERS PER DAC

0

255

511

DELTA-SIGMA DACs

767

1023

EACH OFFSET REGISTER CAN BE INDEPENDENTLY SET BETWEEN

0 AND 1020. 1020 = 4 x FFh. THIS EXAMPLE ILLUSTRATES POSITIVE

AND NEGATVE TEMPCO.

DAC

LUT

BITS

7:0

F8h

DAC

LUT

BITS

7:0

F9h

DAC

LUT

BITS

7:0

FAh

DAC

LUT

BITS

7:0

FBh

DAC

LUT

BITS

7:0

FCh

DAC

LUT

BITS

7:0

FDh

DAC

LUT

BITS

7:0

FEh

DAC

LUT

BITS

7:0

FFh

0

255

511

-40°C

-8°C

+8°C

+24°C +40°C +56°C +70°C +88°C +104°C

DELTA-SIGMA DACs

767

1023

EACH OFFSET REGISTER CAN BE INDEPENDENTLY

SET BETWEEN 0 AND 1020. 1020 = 4 x FFh. THIS

EXAMPLE ILLUSTRATES POSITIVE TEMPCO.

DAC

LUT

BITS

7:0

F8h

DAC

LUT

BITS

7:0

F9h

DAC

LUT

BITS

7:0

FAh

DAC

LUT

BITS

7:0

FBh

DAC

LUT

BITS

7:0

FCh

DAC

LUT

BITS

7:0

FDh

DAC

LUT

BITS

7:0

FEh

DAC

LUT

BITS

7:0

FFh

DAC OFFSET LUTs (04h/06h)[A2h/B2h]

EIGHT REGISTERS PER DAC

-40°C

-8°C

+8°C

+24°C +40°C +56°C +70°C +88°C +104°C