Adc timing, Right-shifting adc result, Low-voltage operation – Rainbow Electronics DS1876 User Manual

Page 15: Adc timing right-shifting adc result, Figure 4. adc round-robin timing, Ds1876 sfp controller with dual ldd interface

______________________________________________________________________________________ 15

DS1876

SFP Controller with Dual LDD Interface

The ADC results (after right-shifting, if used) are com-

pared to the alarm and warning thresholds after each

conversion, and the corresponding alarms are set that

can be used to trigger the TXFOUT output. These ADC

thresholds are user programmable, as are the masking

registers that can be used to prevent the alarms from trig-

gering the TXFOUT output.

ADC Timing

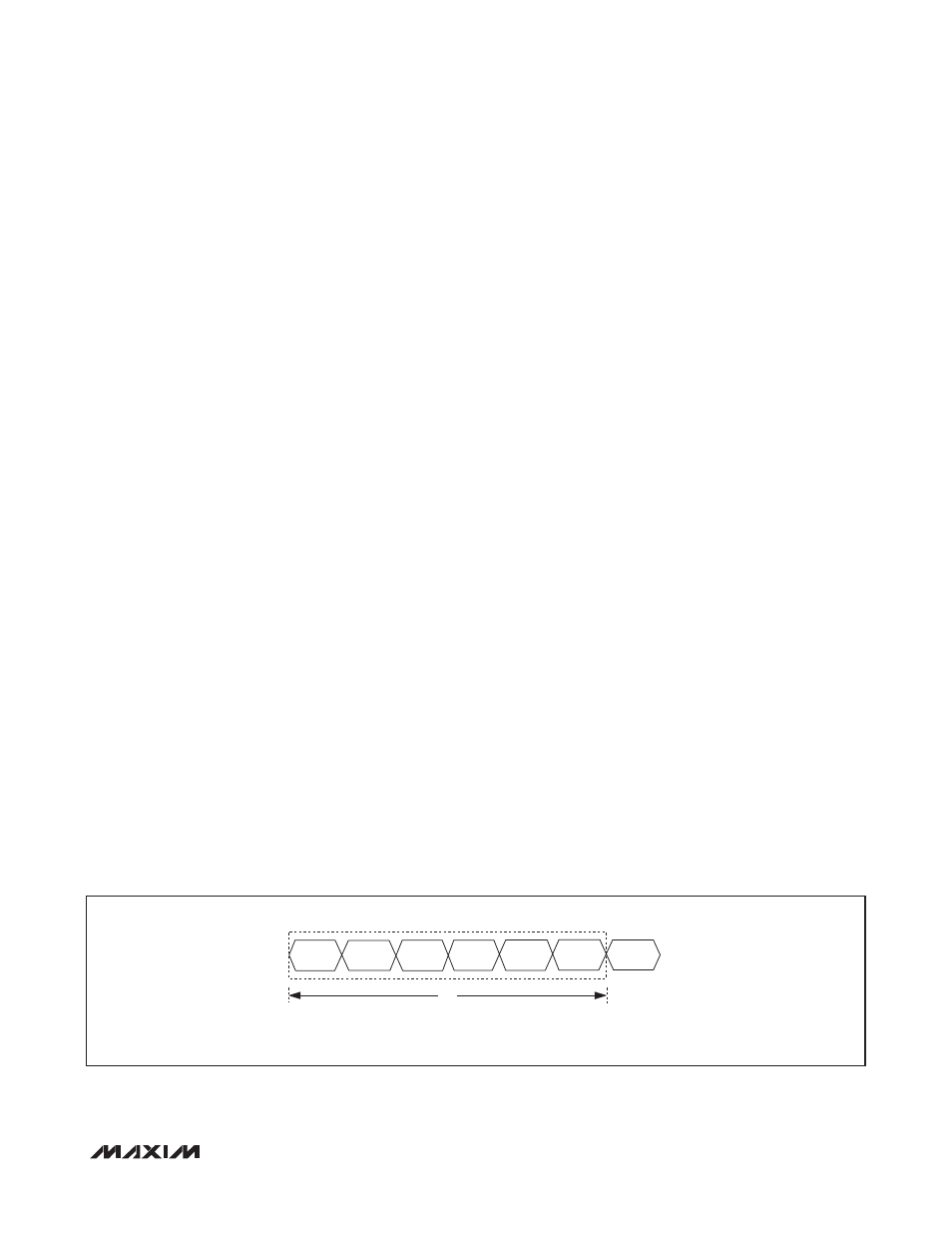

There are six analog channels that are digitized in a

round-robin fashion in the order as shown in Figure 4.

The total time required to convert all six channels is t

RR

(see the Analog Voltage Monitoring Characteristics table

for details).

Right-Shifting ADC Result

If the weighting of the ADC digital reading must conform

to a predetermined full-scale (PFS) value defined by

a standard’s specification (e.g., SFF-8472), then right-

shifting can be used to adjust the PFS analog measure-

ment range while maintaining the weighting of the ADC

results. The DS1876’s range is wide enough to cover all

requirements; when the maximum input value is P 1/2

the FS value, right-shifting can be used to obtain greater

accuracy. For instance, the maximum voltage might be

1/8 the specified PFS value, so only 1/8 of the converter’s

range is effective over this range. An alternative is to cali-

brate the ADC’s full-scale range to 1/8 the readable PFS

value and use a right-shift value of 3. With this implemen-

tation, the resolution of the measurement is increased by

a factor of 8, and because the result is digitally divided

by 8 by right-shifting, the bit weight of the measurement

still meets the standard’s specification (i.e., SFF-8472).

The right-shift operation on the ADC result is carried

out based on the contents of right-shift control registers

(Table 02h, Registers 8Eh

-8Fh) in EEPROM. Four analog

channels—PMON1, PMON2, BMON1, and BMON2—

each have 3 bits allocated to set the number of right-

shifts. Up to seven right-shift operations are allowed and

are executed as a part of every conversion before the

results are compared to the high and low alarm levels, or

loaded into their corresponding measurement registers

(Lower Memory, Registers 64h–6Bh). This is true during

the setup of internal calibration as well as during subse-

quent data conversions.

Low-Voltage Operation

The DS1876 contains two power-on reset (POR) levels.

The lower level is a digital POR (POD) and the higher

level is an analog POR (POA). At startup, before the sup-

ply voltage rises above POA, the outputs are disabled,

all SRAM locations are set to their defaults, shadowed

EEPROM (SEE) locations are zero, and all analog cir-

cuitry is disabled. When V

CC

reaches POA, the SEE is

recalled, and the analog circuitry is enabled. While V

CC

remains above POA, the device is in its normal operating

state, and it responds based on its nonvolatile configu-

ration. If during operation V

CC

falls below POA, but is

still above POD, the SRAM retains the SEE settings from

the first SEE recall, but the device analog is shut down

and the outputs disabled. If the supply voltage recovers

back above POA, the device immediately resumes nor-

mal operation. If the supply voltage falls below POD, the

device SRAM is placed in its default state and another

SEE recall is required to reload the nonvolatile settings.

The EEPROM recall occurs the next time V

CC

next

exceeds POA. Figure 5 shows the sequence of events

as the voltage varies.

Any time V

CC

is above POD, the I

2

C interface can be

used to determine if V

CC

is below the POA level. This

is accomplished by checking the RDYB bit in the status

byte (Lower Memory, Register 6Eh). RDYB is set when

V

CC

is below POA; when V

CC

rises above POA, RDYB

is timed (within 500Fs) to go to 0, at which point the part

is fully functional.

Figure 4. ADC Round-Robin Timing

TEMP

V

CC

BMON1

BMON2

PMON1

PMON2

TEMP

ONE ROUND-ROBIN ADC CYCLE

t

RR

NOTE: IF THE VCC LO ALARM IS ENABLED AT POWER-UP, THE ADC ROUND-ROBIN TIMING CYCLES BETWEEN TEMPERATURE AND V

CC

ONLY UNTIL V

CC

IS ABOVE THE VCC LO

ALARM THRESHOLD. THIS ALSO OCCURS IF THERE ARE BOTH A TXD1 EVENT AND A TXD2 EVENT UNDER THE SAME CONDITIONS AS PREVIOUSLY MENTIONED.