Exttrig* signal, Figure 2-15. exttrig* signal timing, Exttrig* signal -35 – National Instruments AT-MIO-16X User Manual

Page 57: Figure 2-15. exttrig* signal timing -35

Chapter 2

Configuration and Installation

© National Instruments Corporation

2-35

AT-MIO-16X User Manual

EXTTRIG* Signal

Any data acquisition sequence can be initiated by an external trigger

applied to the EXTTRIG* pin. Applying a falling edge to the

EXTTRIG* pin starts the sample and sample-interval counters, thereby

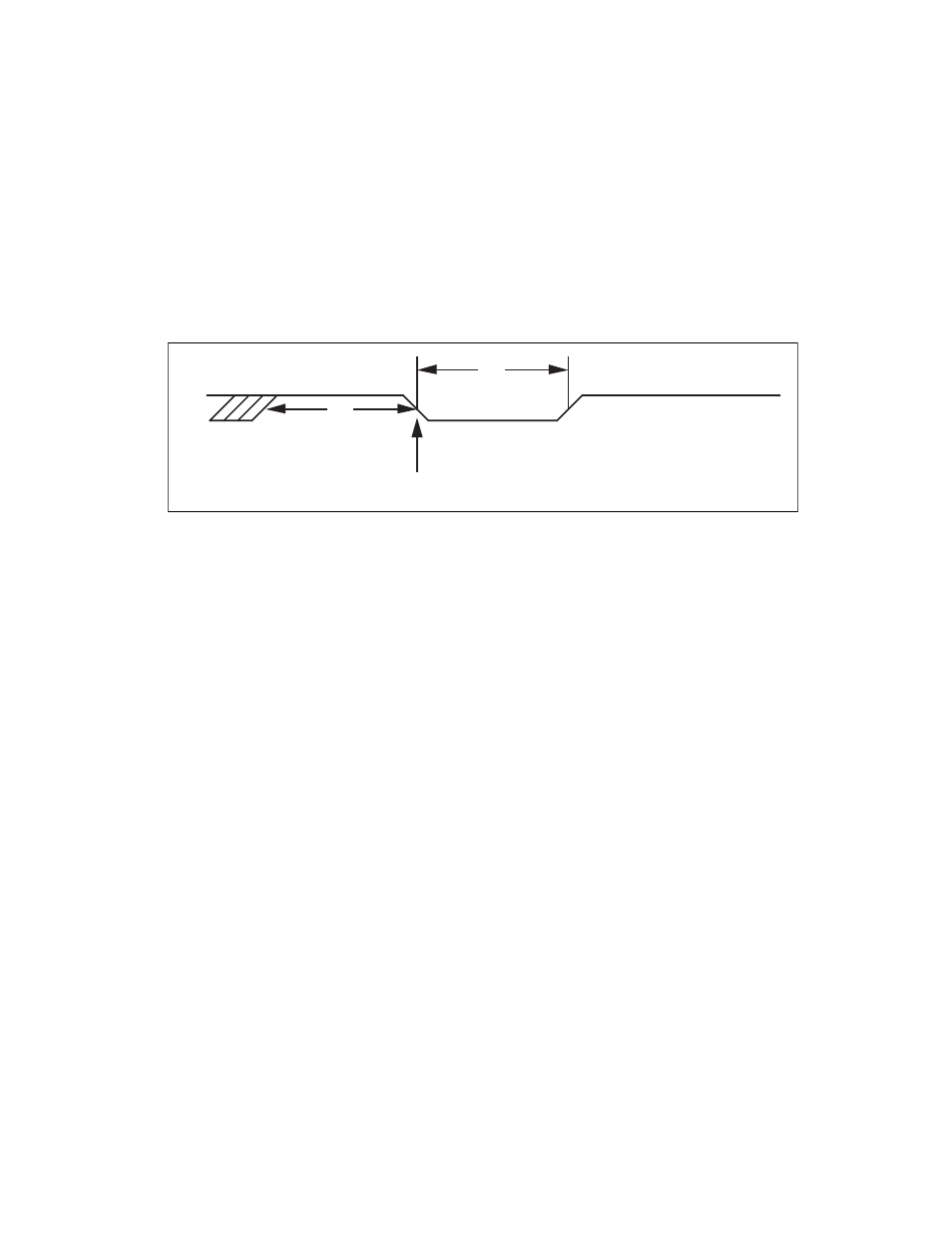

initiating a data acquisition sequence. Figure 2-15 shows the timing

requirements for the EXTTRIG* signal.

Figure 2-15. EXTTRIG* Signal Timing

The EXTTRIG* pin is also used to initiate AT-MIO-16X pretriggered

data acquisition operations. In pretriggered mode, data is acquired after

the first falling edge trigger is received, but no sample counting occurs

until after a second falling edge trigger is applied to the EXTTRIG* pin.

The acquisition then completes when the sample counter decrements to

zero. This mode acquires data both before and after a hardware trigger

is received.

The minimum pulse width allowed is 50 ns. The first A/D conversion

starts within one sample interval from the high-to-low edge. The

sample interval is controlled by Counter 3 or EXTCONV*. There is no

maximum pulse width limitation; however, EXTTRIG* should be high

for at least 50 ns before going low. The EXTTRIG* signal is one HCT

load and is pulled up to +5 V through a 10-k

Ω

resistor.

The EXTTRIG* signal is logically ANDed with the internal

DAQSTART signal. If a data acquisition sequence is to be initiated with

an internal trigger, EXTTRIG* must be high at both the I/O connector

and the RTSI switch. If EXTTRIG* is low, the sequence will not be

triggered. In addition, triggers from the EXTTRIG* signal can be

inhibited through programming of a register in the AT-MIO-16X

register set.

tw 50 nsec minimum

V

IL

VIH

tw

tw

First A/D conversion starts within 1 sample interval from this point