National Instruments AT-MIO-16X User Manual

Page 114

Chapter 4

Register Map and Descriptions

AT-MIO-16X User Manual

4-18

© National Instruments Corporation

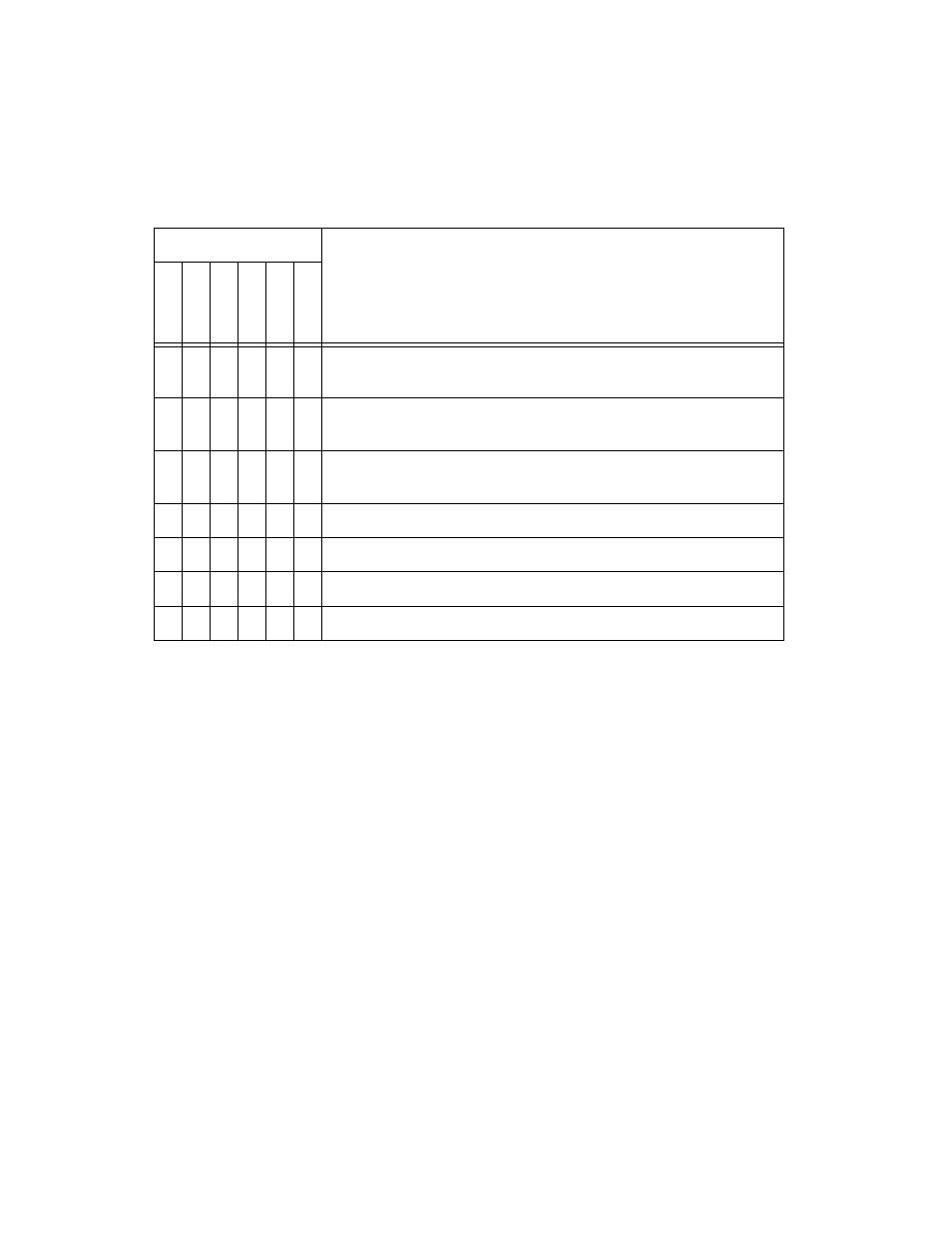

5

DAC1REQ

DAC 1 Request Enable—This bit

controls DMA requesting and interrupt

generation from D/A updates. If this bit

is set, an interrupt or DMA request is

generated when the DAC is ready to

receive data. If this bit is cleared, no

DMA request or interrupt is generated.

To select a specific mode, refer to

Table 4-3 for available modes and

associated bit patterns.

4

DAC0REQ

DAC 0 Request Enable—This bit

controls DMA requesting and interrupt

generation from D/A updates. If this bit

is set, an interrupt or DMA request is

generated when the DAC is ready to

receive data. If this bit is cleared, no

DMA request or interrupt is generated.

To select a specific mode, refer to

1

1

1

0

0

1

Channel A and Channel B to DAC0 (double-buffered) with ADC

interrupt

1

1

1

0

1

0

Channel A and Channel B to DAC1 (double-buffered) with ADC

interrupt

1

1

1

0

1

1

Channels A and B to DACs 0 and 1 (sync double-channel) with ADC

interrupt

1

1

1

1

0

0

Channels A and B from ADC (double-buffered) with timer interrupt

1

1

1

1

0

1

Channel A to DAC0 and Channel B from ADC

1

1

1

1

1

0

Channel A to DAC1 and Channel B from ADC

1

1

1

1

1

1

Channel A to DAC0 and DAC1 (interleaved) and Channel B from ADC

Table 4-3. DMA and Interrupt Modes (Continued)

Interface Mode

Mode Description

IO_

IN

T

DM

ACHA

DM

ACHB

A

DCRE

Q

DAC1REQ

DAC0REQ