Table 4-3. dma and interrupt modes, Table 4-3, Dma and interrupt modes -16 – National Instruments AT-MIO-16X User Manual

Page 112

Chapter 4

Register Map and Descriptions

AT-MIO-16X User Manual

4-16

© National Instruments Corporation

6

ADCREQ

ADC Request Enable—This bit controls

DMA requesting and interrupt

generation from an A/D conversion.

If this bit is set, an interrupt or DMA

request is generated when an A/D

conversion is available in the FIFO. If

this bit is cleared, no DMA request or

interrupt is generated following an A/D

conversion. To select a specific mode,

refer to Table 4-3 for available modes

and associated bit patterns.

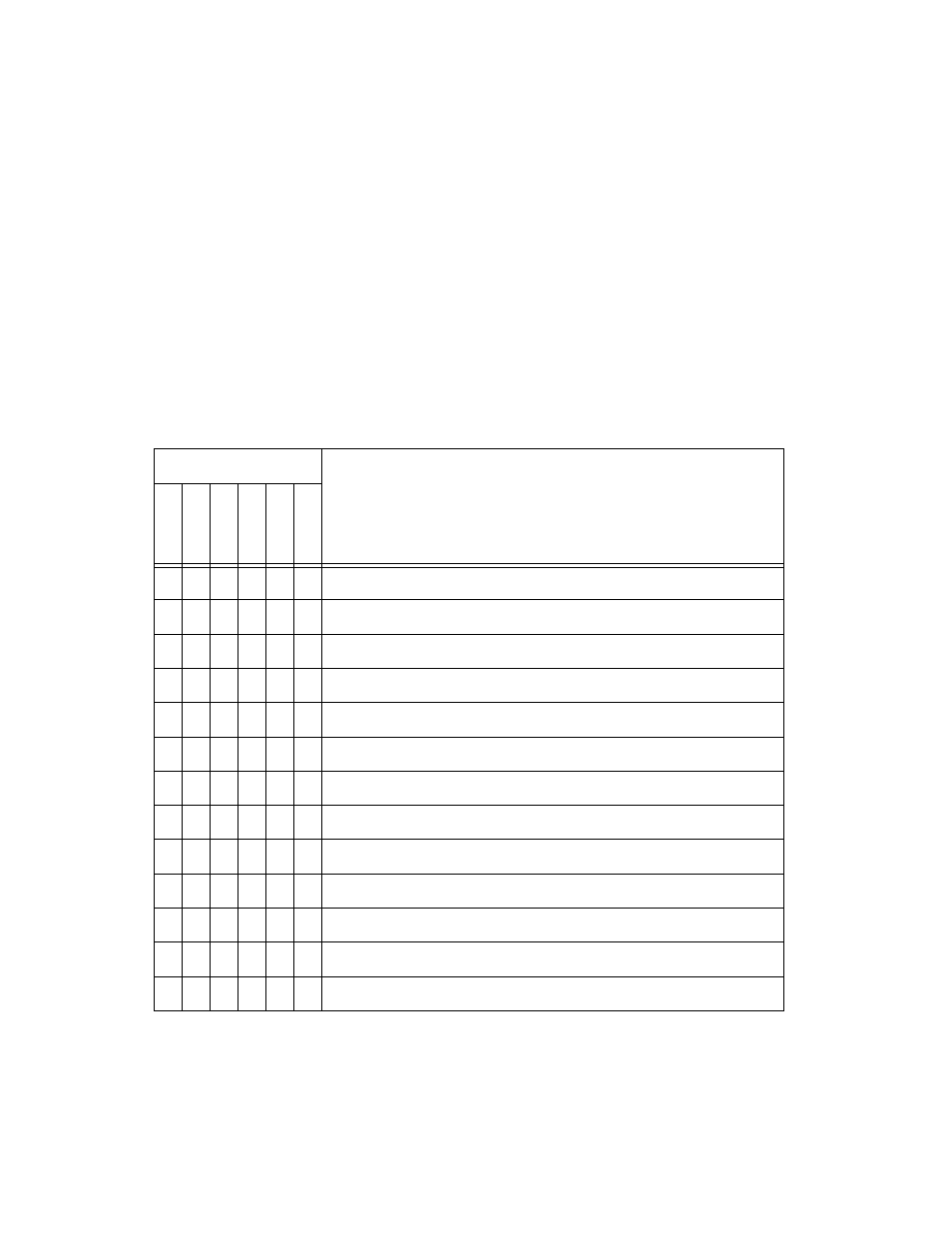

Table 4-3. DMA and Interrupt Modes

Interface Mode

Mode Description

IO

_

INT

DMAC

H

A

DM

ACHB

ADCR

EQ

DA

C1

RE

Q

DA

C0

RE

Q

0

1

0

0

0

1

Channel A to DAC0

0

1

0

0

1

0

Channel A to DAC1

0

1

0

0

1

1

Channel A to DAC0 and DAC1 (interleaved)

0

1

0

1

0

0

Channel A from ADC

0

0

1

0

0

1

Channel B to DAC0

0

0

1

0

1

0

Channel B to DAC1

0

0

1

0

1

1

Channel B to DAC0 and DAC1 (interleaved)

0

0

1

1

0

0

Channel B from ADC

0

1

1

0

0

0

Channel A and Channel B to DAC0 and DAC1 (double-buffered)

0

1

1

0

0

1

Channel A and Channel B to DAC0 (double-buffered)

0

1

1

0

1

0

Channel A and Channel B to DAC1 (double-buffered)

0

1

1

0

1

1

Channel A and Channel B to DAC0 and DAC1 (sync double-channel)

0

1

1

1

0

0

Channel A and Channel B from ADC (double-buffered)