Status register 1, Status register 1 -25 – National Instruments AT-MIO-16X User Manual

Page 121

Chapter 4

Register Map and Descriptions

© National Instruments Corporation

4-25

AT-MIO-16X User Manual

Status Register 1

Status Register 1 contains 16 bits of AT-MIO-16X hardware status

information, including interrupt, analog input status, analog output

status, and data acquisition progress.

Address:

Base address + 18 (hex)

Type:

Read-only

Word Size:

16-bit

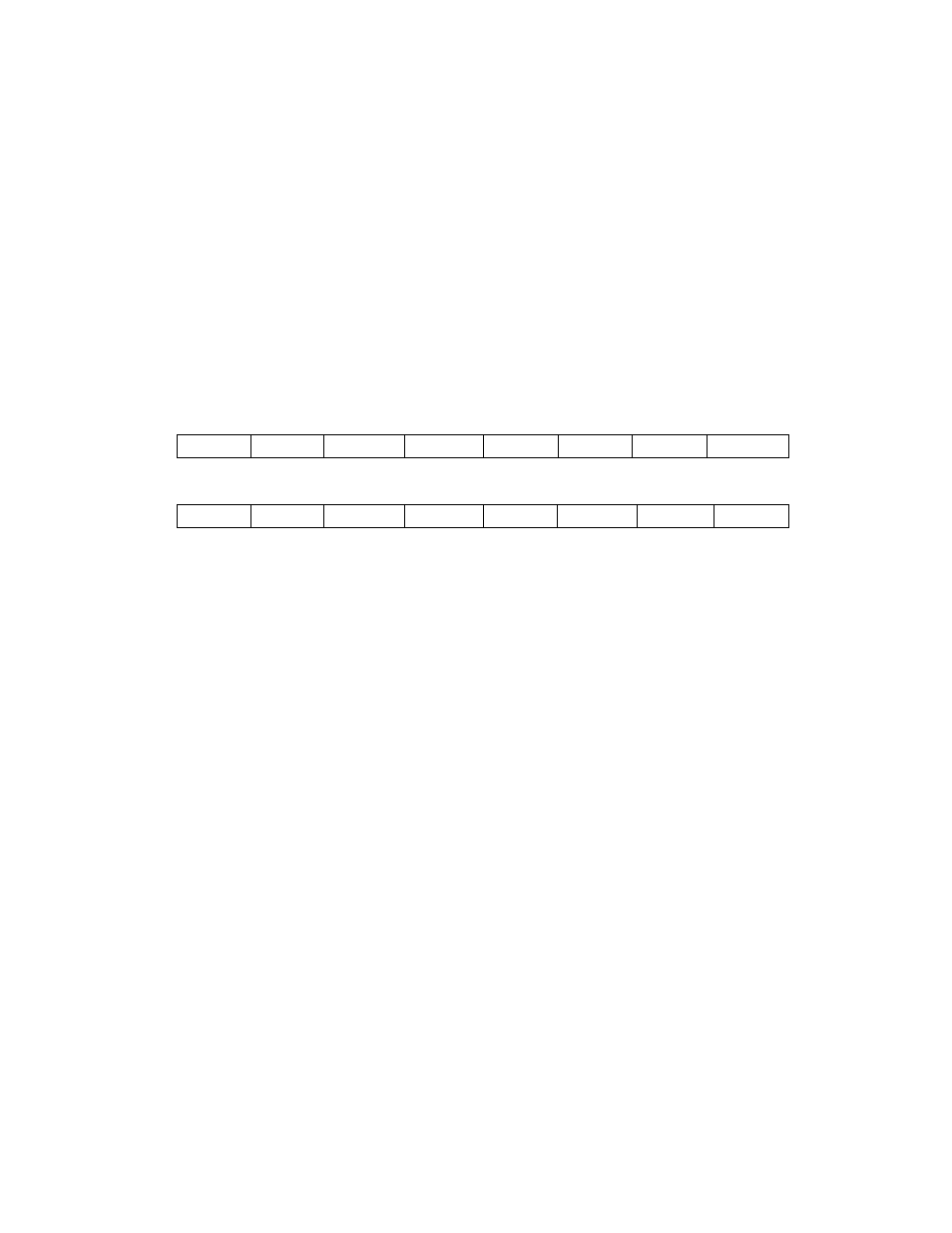

Bit Map:

Bit

Name

Description

15

DAQCOMP

Data Acquisition Complete—This bit

reflects the status of the data acquisition

termination signal. If DAQCOMP is set

and either OVERFLOW or OVERRUN

is also set, the current acquisition

sequence ended on an error condition.

If DAQCOMP is set and neither

OVERFLOW nor OVERRUN is set, the

data acquisition operation has completed

without error. When DAQCOMP is set,

and ADCREQ in Command Register 3 is

also set, enabled interrupt or DMA

requests are generated until the ADC

FIFO is empty. DAQCOMP is cleared by

strobing the DAQ Clear Register.

14

DAQPROG

Data Acquisition Progress—This bit

indicates whether a data acquisition

operation is in progress. If DAQPROG

is set, a data acquisition operation is in

progress. If DAQPROG is cleared, the

7

6

5

DACCOMP

4

3

DAQFIFOHF*

2

EEPROMDATA

1

0

EEPROMCD*

TMRREQ

DAQFIFOFF*

CFGMEMEF*

DAQFIFOEF*

15

MSB

LSB

14

13

DAQPROG

12

11

ADCFIFOEF*

10

DMATCB

9

8

OVERFLOW

DAQCOMP

ADCFIFOHF*

OVERRUN

DMATCA