Timing connections for data acquisition and analog, Scanclk signal, Extstrobe* signal – National Instruments AT-MIO-16X User Manual

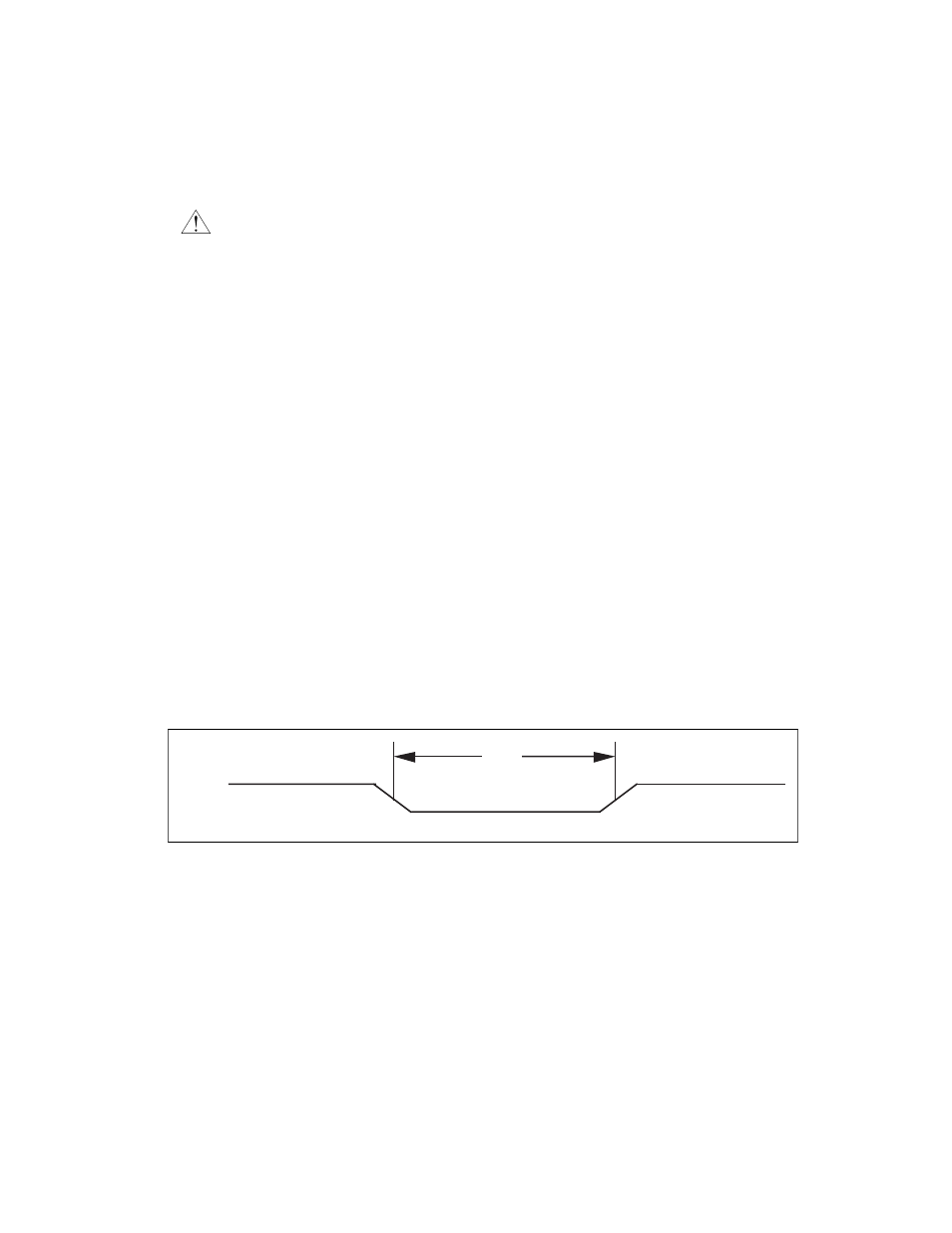

Page 55: Figure 2-13. extstrobe* signal timing, Scanclk signal -33 extstrobe* signal -33, Figure 2-13. extstrobe* signal timing -33

Chapter 2

Configuration and Installation

© National Instruments Corporation

2-33

AT-MIO-16X User Manual

Caution:

Under no circumstances should these +5-V power pins be directly

connected to analog or digital ground or to any other voltage source on the

AT-MIO-16X or any other device. Doing so can damage the AT-MIO-16X

and the PC. National Instruments is not liable for damages resulting from

such a connection.

Timing Connections for Data Acquisition and Analog Output

The data acquisition and analog output timing signals are SCANCLK,

EXTSTROBE*, EXTCONV*, EXTTRIG*, EXTGATE*, and

EXTTMRTRIG*.

SCANCLK Signal

SCANCLK is an output signal that generates a low-to-high edge

whenever an A/D conversion begins. SCANCLK pulses only when

scanning is enabled on the AT-MIO-16X. SCANCLK is normally

low and pulses high for approximately 8 conversion begins. The

low-to-high edge can be used to clock external analog input

multiplexers. The SCANCLK signal is driven by one CMOS TTL gate.

EXTSTROBE* Signal

A low pulse of no less than 500 ns is generated on the EXTSTROBE*

pin when the External Strobe Register is accessed. See the External

Strobe Register section in Chapter 4, Register Map and Descriptions,

for more information. Figure 2-13 shows the timing for the

EXTSTROBE* signal.

Figure 2-13. EXTSTROBE* Signal Timing

The pulse width is defined as 500 ns minimum. The EXTSTROBE*

signal can be used by an external device to latch signals or trigger

events. The EXTSTROBE* signal is an HCT signal.

tw 500 nsec

VOH

tw

V

OL

-