8 i/o memory of programmable timer – Epson S1C63558 User Manual

Page 81

S1C63558 TECHNICAL MANUAL

EPSON

71

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Programmable Timer)

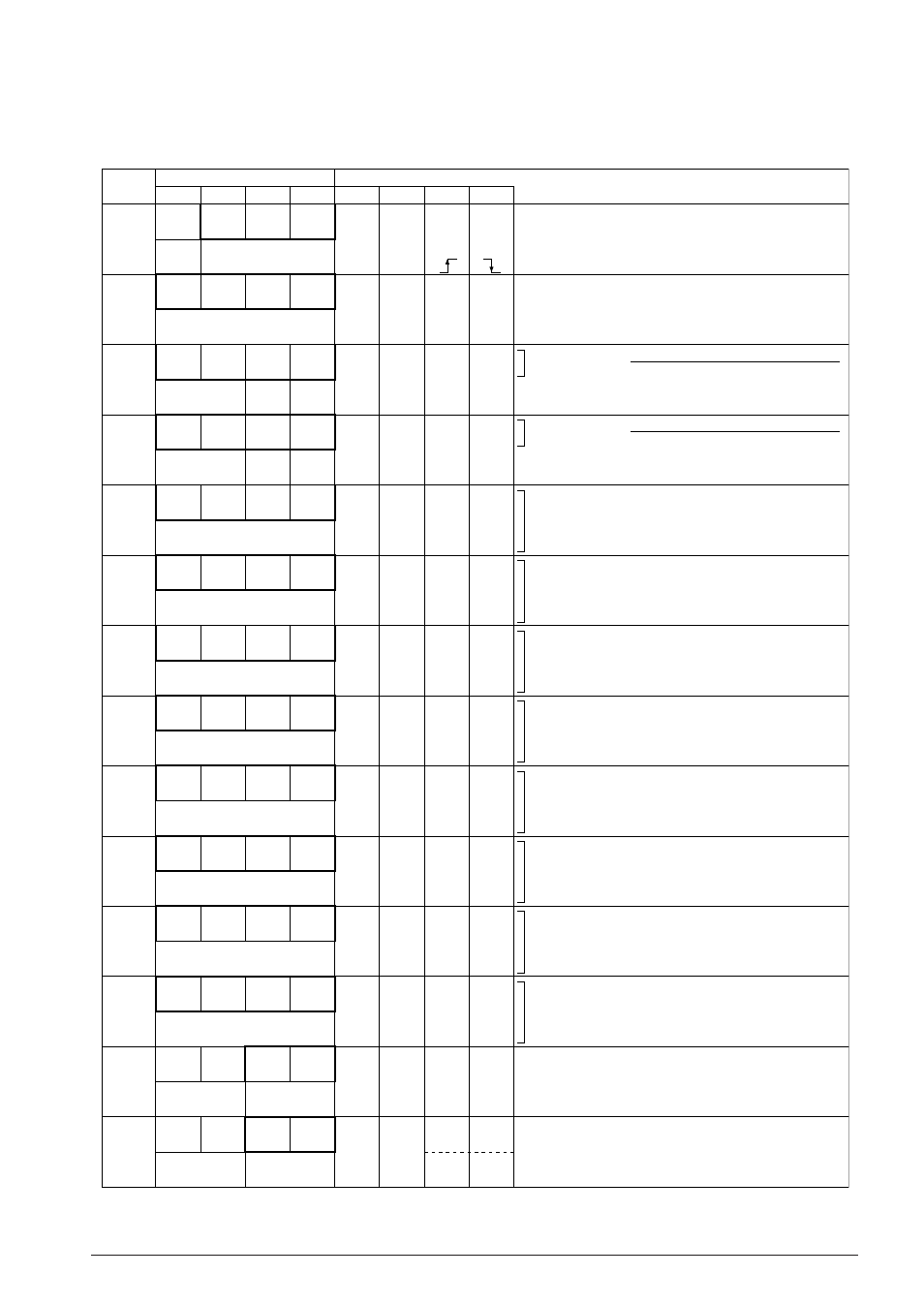

4.10.8 I/O memory of programmable timer

Table 4.10.8.1 shows the I/O addresses and the control bits for the programmable timer.

Table 4.10.8.1 Control bits of programmable timer

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

CHSEL

PTOUT

CKSEL1

CKSEL0

0

0

0

0

Timer1

On

OSC3

OSC3

Timer0

Off

OSC1

OSC1

TOUT output channel selection

TOUT output control

Prescaler 1 source clock selection

Prescaler 0 source clock selection

R/W

FFC1H

CHSEL PTOUT CKSEL1 CKSEL0

PTPS01

PTPS00

PTRST0

∗

3

PTRUN0

0

0

–

∗

2

0

Reset

Run

Invalid

Stop

Prescaler 0

division ratio

selection

Timer 0 reset (reload)

Timer 0 Run/Stop

W

R/W

R/W

FFC2H

PTPS01 PTPS00 PTRST0 PTRUN0

0

∗

3

EVCNT

FCSEL

PLPOL

–

∗

2

0

0

0

Event ct.

With NR

Timer

No NR

Unused

Timer 0 counter mode selection

Timer 0 function selection (for event counter mode)

Timer 0 pulse polarity selection (for event counter mode)

R

R/W

FFC0H

0

EVCNT FCSEL

PLPOL

0

1/1

1

1/4

2

1/32

3

1/256

[PTPS01, 00]

Division ratio

PTPS11

PTPS10

PTRST1

∗

3

PTRUN1

0

0

–

∗

2

0

Reset

Run

Invalid

Stop

Prescaler 1

division ratio

selection

Timer 1 reset (reload)

Timer 1 Run/Stop

W

R/W

R/W

FFC3H

PTPS11 PTPS10 PTRST1 PTRUN1

RLD03

RLD02

RLD01

RLD00

0

0

0

0

MSB

Programmable timer 0 reload data (low-order 4 bits)

LSB

R/W

FFC4H

RLD03

RLD02

RLD01

RLD00

RLD07

RLD06

RLD05

RLD04

0

0

0

0

MSB

Programmable timer 0 reload data (high-order 4 bits)

LSB

R/W

FFC5H

RLD07

RLD06

RLD05

RLD04

RLD13

RLD12

RLD11

RLD10

0

0

0

0

MSB

Programmable timer 1 reload data (low-order 4 bits)

LSB

R/W

FFC6H

RLD13

RLD12

RLD11

RLD10

RLD17

RLD16

RLD15

RLD14

0

0

0

0

MSB

Programmable timer 1 reload data (high-order 4 bits)

LSB

R/W

FFC7H

RLD17

RLD16

RLD15

RLD14

PTD03

PTD02

PTD01

PTD00

0

0

0

0

MSB

Programmable timer 0 data (low-order 4 bits)

LSB

R

FFC8H

PTD03

PTD02

PTD01

PTD00

PTD07

PTD06

PTD05

PTD04

0

0

0

0

MSB

Programmable timer 0 data (high-order 4 bits)

LSB

R

FFC9H

PTD07

PTD06

PTD05

PTD04

PTD13

PTD12

PTD11

PTD10

0

0

0

0

MSB

Programmable timer 1 data (low-order 4 bits)

LSB

R

FFCAH

PTD13

PTD12

PTD11

PTD10

PTD17

PTD16

PTD15

PTD14

0

0

0

0

MSB

Programmable timer 1 data (high-order 4 bits)

LSB

R

FFCBH

PTD17

PTD16

PTD15

PTD14

0

1/1

1

1/4

2

1/32

3

1/256

[PTPS11, 10]

Division ratio

FFE2H

0

0

EIPT1

EIPT0

R

R/W

0

∗

3

0

∗

3

EIPT1

EIPT0

–

∗

2

–

∗

2

0

0

Enable

Enable

Mask

Mask

Unused

Unused

Interrupt mask register (Programmable timer 1)

Interrupt mask register (Programmable timer 0)

FFF2H

0

0

IPT1

IPT0

R

R/W

0

∗

3

0

∗

3

IPT1

IPT0

–

∗

2

–

∗

2

0

0

(R)

Yes

(W)

Reset

(R)

No

(W)

Invalid

Unused

Unused

Interrupt factor flag (Programmable timer 1)

Interrupt factor flag (Programmable timer 0)

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read