3 cpu, rom, ram, 1 cpu, 2 code rom – Epson S1C63558 User Manual

Page 22: 3 ram, Chapter

12

EPSON

S1C63558 TECHNICAL MANUAL

CHAPTER 3: CPU, ROM, RAM

CHAPTER

3 CPU, ROM, RAM

3.1 CPU

The S1C63558 has a 4-bit core CPU S1C63000 built-in as its CPU part.

Refer to the "S1C63000 Core CPU Manual" for the S1C63000.

Note:

The SLP instruction cannot be used because the SLEEP operation is not assumed in the S1C63558.

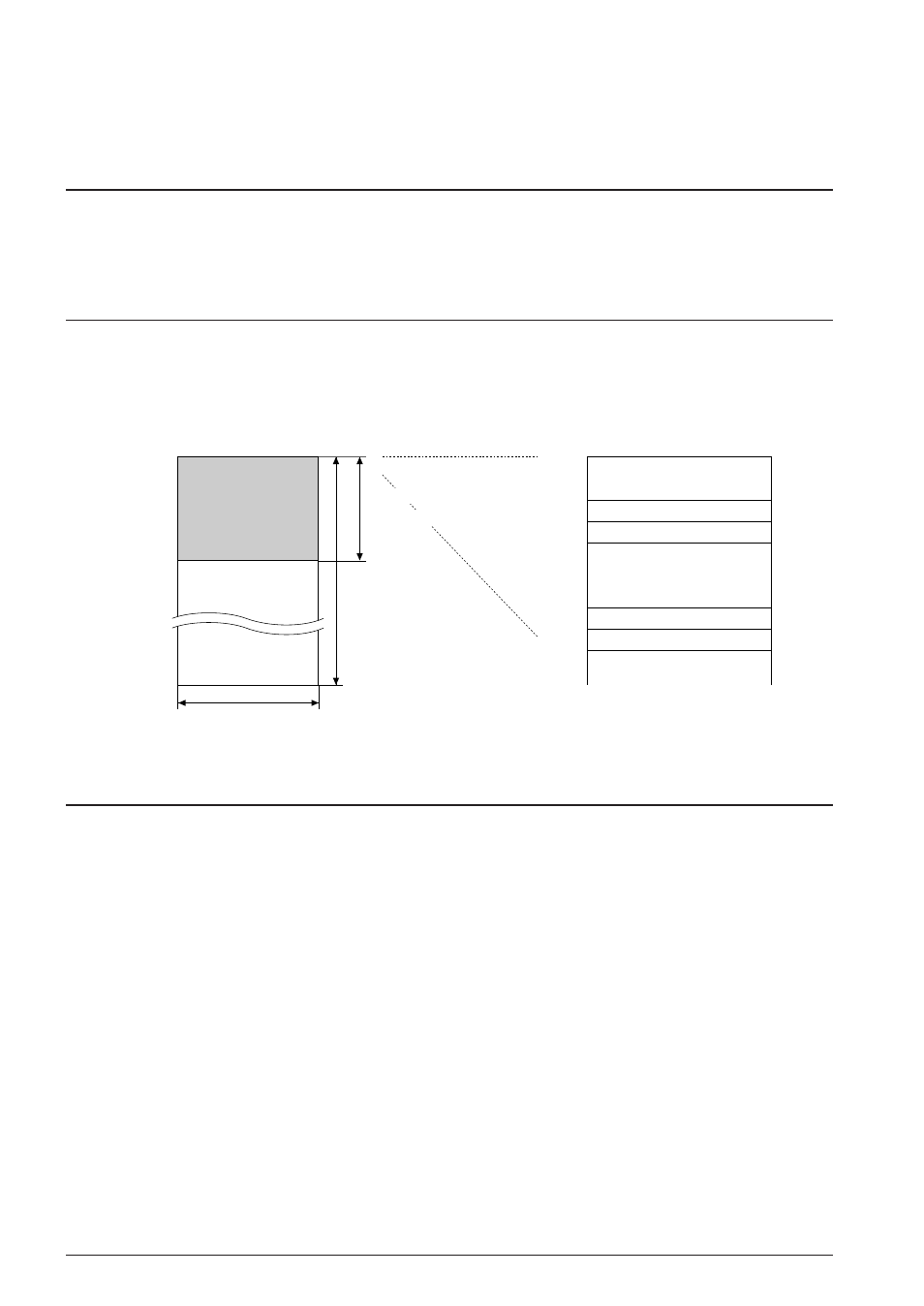

3.2 Code ROM

The built-in code ROM is a mask ROM for loading programs, and has a capacity of 8,192 steps

×

13 bits.

The core CPU can linearly access the program space up to step FFFFH from step 0000H, however, the

program area of the S1C63558 is step 0000H to step 1FFFH. The program start address after initial reset is

assigned to step 0110H. The non-maskable interrupt (NMI) vector and hardware interrupt vectors are

allocated to step 0100H and steps 0104H–010EH, respectively.

0000H

1FFFH

2000H

FFFFH

0000H

0100H

0104H

010EH

0110H

Program area

NMI vector

Hardware

interrupt vectors

Program start address

Program area

ROM

Unused area

13 bits

S1C63000 core CPU

program space

S1C63558

program area

Fig. 3.2.1 Configuration of code ROM

3.3 RAM

The RAM is a data memory for storing various kinds of data, and has a capacity of 5,120 words

×

4 bits.

The RAM area is assigned to addresses 0000H to 13FFH on the data memory map. Addresses 0100H to

01FFH are 4-bit/16-bit data accessible areas and in other areas it is only possible to access 4-bit data.

When programming, keep the following points in mind.

(1) Part of the RAM area is used as a stack area for subroutine call and register evacuation, so pay

attention not to overlap the data area and stack area.

(2) The S1C63000 core CPU handles the stack using the stack pointer for 4-bit data (SP2) and the stack

pointer for 16-bit data (SP1).

16-bit data are accessed in stack handling by SP1, therefore, this stack area should be allocated to the

area where 4-bit/16-bit access is possible (0100H to 01FFH). The stack pointers SP1 and SP2 change

cyclically within their respective range: the range of SP1 is 0000H to 03FFH and the range of SP2 is

0000H to 00FFH. Therefore, pay attention to the SP1 value because it may be set to 0200H or more

exceeding the 4-bit/16-bit accessible range in the S1C63558 or it may be set to 00FFH or less. Memory

accesses except for stack operations by SP1 are 4-bit data access.

After initial reset, all the interrupts including NMI are masked until both the stack pointers SP1 and

SP2 are set by software. Further, if either SP1 or SP2 is re-set when both are set already, the interrupts

including NMI are masked again until the other is re-set. Therefore, the settings of SP1 and SP2 must

be done as a pair.