3 i/o memory of watchdog timer, 4 programming notes – Epson S1C63558 User Manual

Page 34

24

EPSON

S1C63558 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Watchdog Timer)

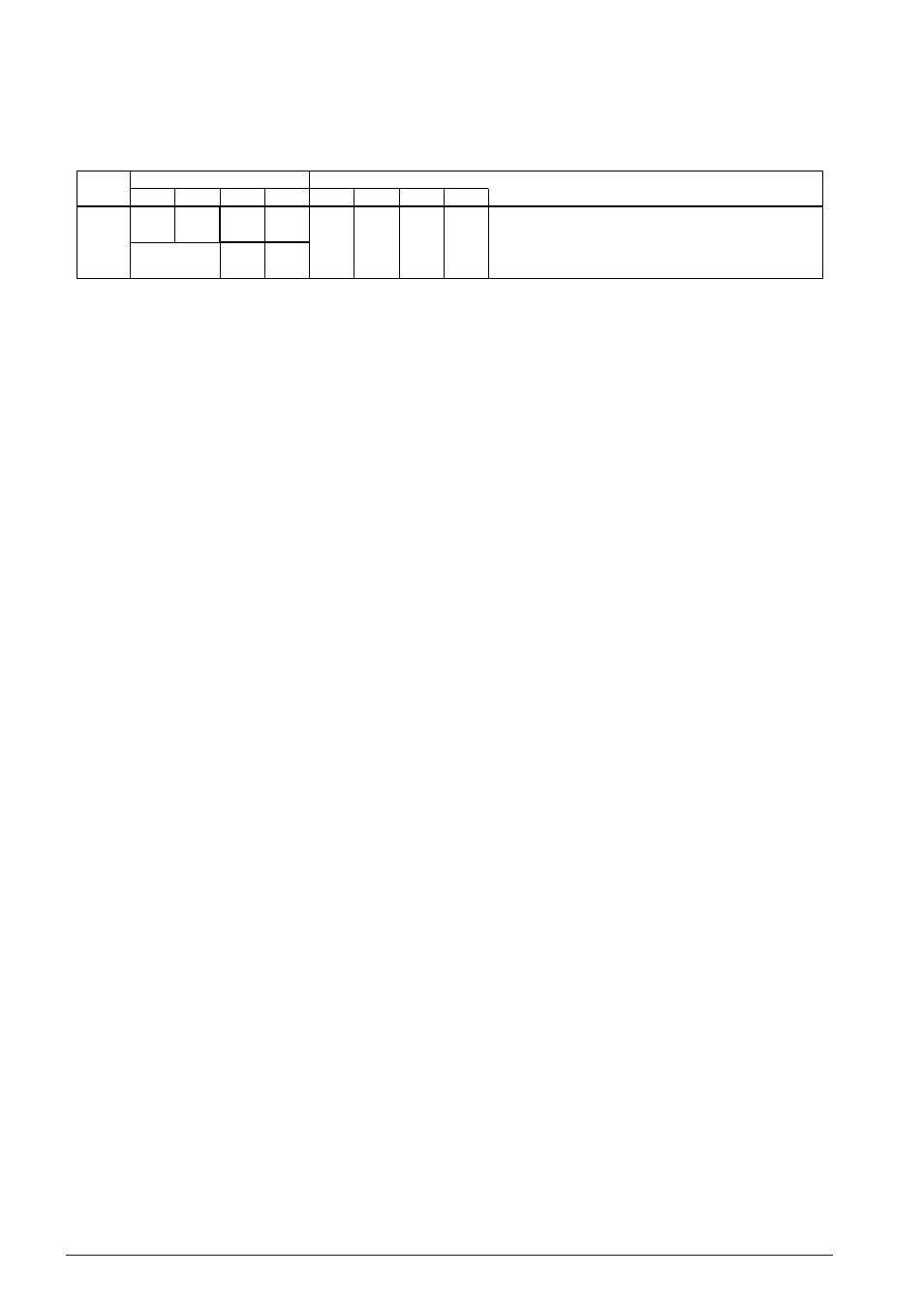

4.2.3 I/O memory of watchdog timer

Table 4.2.3.1 shows the I/O address and control bits for the watchdog timer.

Table 4.2.3.1 Control bits of watchdog timer

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FF07H

0

0

WDEN WDRST

R/W

W

R

0

∗

3

0

∗

3

WDEN

WDRST

∗

3

–

∗

2

–

∗

2

1

Reset

Enable

Reset

Disable

Invalid

Unused

Unused

Watchdog timer enable

Watchdog timer reset (writing)

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read

WDEN: Watchdog timer enable register (FF07H•D1)

Selects whether the watchdog timer is used (enabled) or not (disabled).

When "1" is written: Enabled

When "0" is written: Disabled

Reading: Valid

When "1" is written to the WDEN register, the watchdog timer starts count operation. When "0" is written,

the watchdog timer does not count and does not generate the interrupt (NMI).

At initial reset, this register is set to "1".

WDRST: Watchdog timer reset (FF07H•D0)

Resets the watchdog timer.

When "1" is written: Watchdog timer is reset

When "0" is written: No operation

Reading: Always "0"

When "1" is written to WDRST, the watchdog timer is reset and restarts immediately after that. When "0"

is written, no operation results.

This bit is dedicated for writing, and is always "0" for reading.

4.2.4 Programming notes

(1) When the watchdog timer is being used, the software must reset it within 3-second cycles.

(2) Because the watchdog timer is set in operation state by initial reset, set the watchdog timer to disabled

state (not used) before generating an interrupt (NMI) if it is not used.