Epson S1C63558 User Manual

Page 28

18

EPSON

S1C63558 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

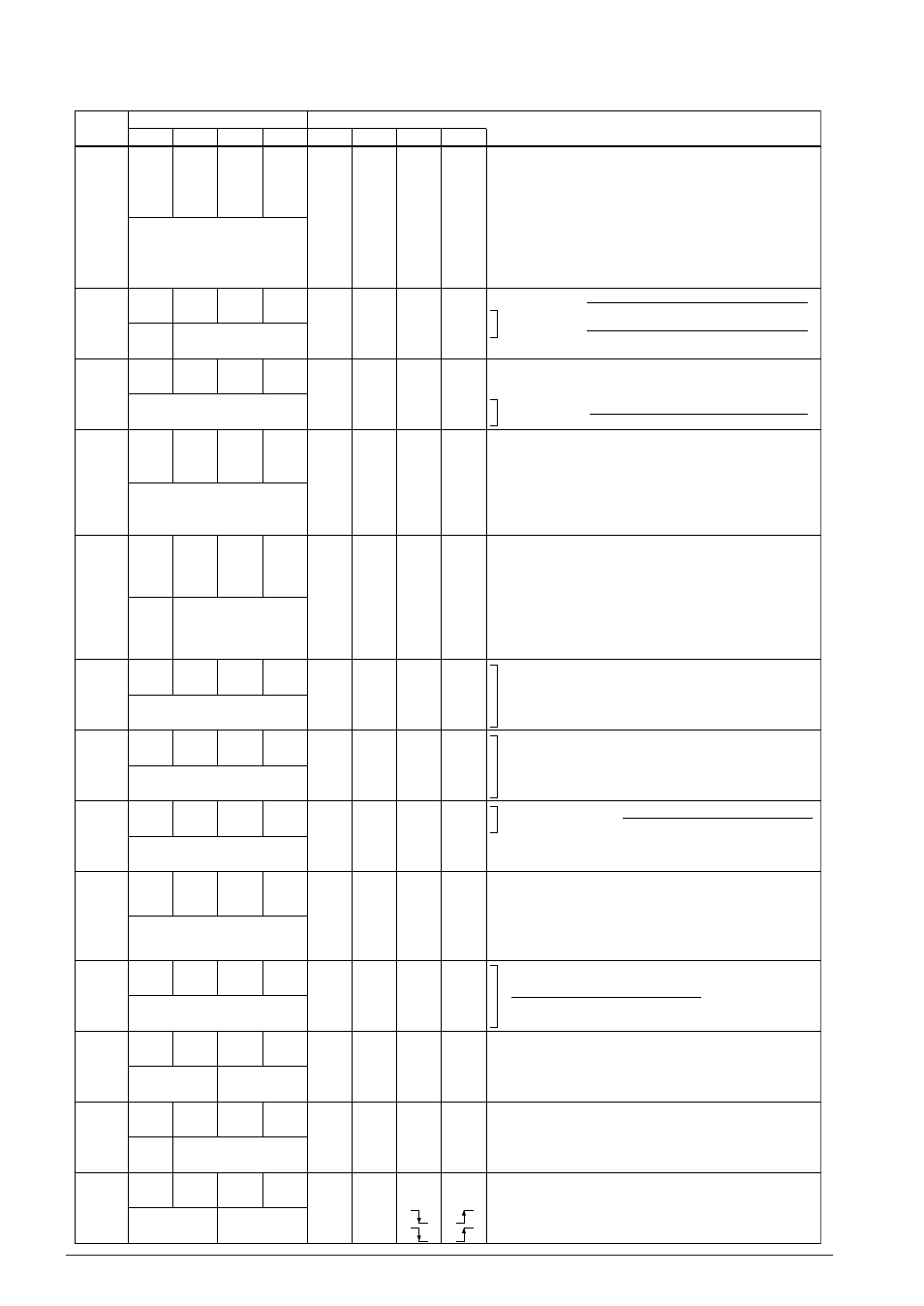

Table 4.1.1 (d) I/O memory map (FF4EH–FF67H)

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FF4EH

R/W

–

∗

2

–

∗

2

–

∗

2

–

∗

2

High

High

High

High

Low

Low

Low

Low

P33 I/O port data

General-purpose register when SIF (clock sync. slave) is selected

P32 I/O port data

General-purpose register when SIF (clock sync.) is selected

P31 I/O port data (ESIFS=0)

General-purpose register when SIF is selected

P30 I/O port data (ESIFS=0)

General-purpose register when SIF is selected

0

Clk-sync. master

2

Async. 7-bit

1

Clk-sync. slave

3

Async. 8-bit

[SMD1S, 0S]

Mode

[SMD1S, 0S]

Mode

FF58H

0

R

R/W

–

∗

2

0

0

0

SIF

I/O

Unused

Serial I/F (2)

mode selection

Serial I/F (2) enable (P3x port function selection)

0

1200bps

1

600bps

2

2400bps

3

PT

[SCS1S, 0S]

Mode

FF59H

R/W

0

0

0

0

Enable

Odd

Disable

Even

Serial I/F (2) parity enable register

Serial I/F (2) parity mode selection

SIF (2) clock

source selection

R/W

FF5AH

0

0

0

0

Run

Trigger

Enable

Run

Trigger

Enable

Stop

–

Disable

Stop

–

Disable

Serial I/F (2) receive status (reading)

Serial I/F (2) receive trigger (writing)

Serial I/F (2) receive enable

Serial I/F (2) transmit status (reading)

Serial I/F (2) transmit trigger (writing)

Serial I/F (2) transmit enable

R

R/W

FF5BH

–

∗

2

0

0

0

Error

Reset

Error

Reset

Error

Reset

No error

–

No error

–

No error

–

Unused

Serial I/F (2) framing error flag status (reading)

Serial I/F (2) framing error flag reset (writing)

Serial I/F (2) parity error flag status (reading)

Serial I/F (2) parity error flag reset (writing)

Serial I/F (2) overrun error flag status (reading)

Serial I/F (2) overrun error flag reset (writing)

R/W

FF5CH

–

∗

2

–

∗

2

–

∗

2

–

∗

2

High

High

High

High

Low

Low

Low

Low

Serial I/F (2) t

ransmit/receive data

(low-order 4 bits)

LSB

R/W

FF5DH

–

∗

2

–

∗

2

–

∗

2

–

∗

2

High

High

High

High

Low

Low

Low

Low

MSB

Serial I/F (2) t

ransmit/receive data

(high-order 4 bits)

FF60H

LDUTY1 LDUTY0 Dummy

LPWR

R/W

LDUTY1

LDUTY0

Dummy

LPWR

0

0

0

0

On

Off

LCD drive duty

switch

General-purpose register

LCD power On/Off

0

1/17

1

1/16

2, 3

1/8

[LDUTY1, 0]

Duty

FF61H

EXLCDC ALOFF

ALON

LPAGE

R/W

EXLCDC

ALOFF

ALON

LPAGE

0

1

0

0

Enable

All Off

All On

F100-F15F

Disable

Normal

Normal

F000-F05F

Expanded LCD driver signal control

LCD all Off control

LCD all On control

Display memory area selection (when 1/8 duty is selected)

General-purpose register when 1/16, 1/17 duty is selected

FF62H

LC3

LC2

LC1

LC0

R/W

LC3

LC2

LC1

LC0

–

∗

2

–

∗

2

–

∗

2

–

∗

2

FF65H

0

0

BZOUT XBZOUT

R

R/W

0

∗

3

0

∗

3

BZOUT

XBZOUT

–

∗

2

–

∗

2

0

0

BZ

XBZ

DC

DC

Unused

Unused

R01 output selection (R01 should be fixed at "1".)

R00 output selection (R00 should be fixed at "1".)

FF66H

FSKON

0

RDET

CDET

R/W

R

FSKON

0

∗

3

RDET

CDET

0

–

∗

2

–

∗

4

0

On

Ring

Carrier

Off

No Ring

No Carrier

FSK demodulator On/Off

Unused

Ring detection bit

Carrier detection bit

FF67H

0

0

RDETCP CDETCP

R

R/W

0

∗

3

0

∗

3

RDETCP

CDETCP

–

∗

2

–

∗

2

0

0

Unused

Unused

RDET comparison register

CDET comparison register

0

Light

–

–

15

Dark

[LC3–0]

Contrast

LCD contrast adjustment

P33

(XSRDYS)

P32

(XSCLKS)

P31

(SOUTS)

P30

(SINS)

P33

P32

P31

P30

SMD1S SMD0S

ESIFS

0

∗

3

SMD1S

SMD0S

ESIFS

EPRS

PMDS

SCS1S SCS0S

EPRS

PMDS

SCS1S

SCS0S

RXTRGS RXENS TXTRGS TXENS

RXTRGS

RXENS

TXTRGS

TXENS

0

FERS

PERS

OERS

0

∗

3

FERS

PERS

OERS

TRXD3S TRXD2S TRXD1S TRXD0S

TRXD3S

TRXD2S

TRXD1S

TRXD0S

TRXD7S TRXD6S TRXD5S TRXD4S

TRXD7S

TRXD6S

TRXD5S

TRXD4S