4 i/o memory of svd circuit – Epson S1C63558 User Manual

Page 120

110

EPSON

S1C63558 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (SVD Circuit)

When the SVDON register is set to "1", source voltage or external voltage detection by the SVD circuit is

executed. As soon as the SVDON register is reset to "0", the result is loaded to the SVDDT latch and the

SVD circuit goes OFF.

To obtain a stable detection result, the SVD circuit must be ON for at least l00 µsec. So, to obtain the SVD

detection result, follow the programming sequence below.

1. Set SVDON to "1"

2. Maintain for 100 µsec minimum

3. Set SVDON to "0"

4. Read SVDDT

When the SVD circuit is ON, the IC draws a large current, so keep the SVD circuit off unless it is.

4.13.4 I/O memory of SVD circuit

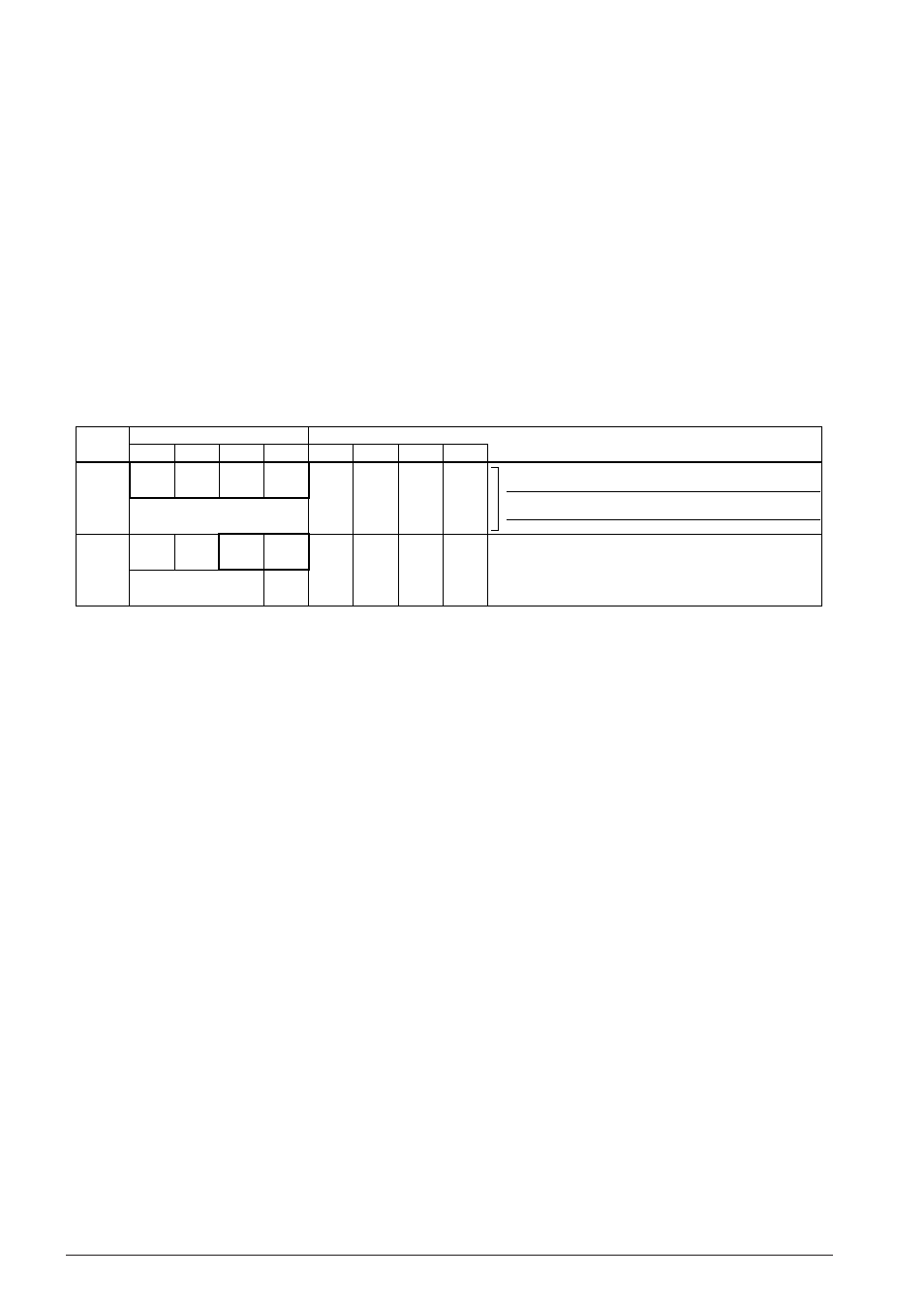

Table 4.13.4.1 shows the I/O addresses and the control bits for the SVD circuit.

Table 4.13.4.1 Control bits of SVD circuit

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FF05H

0

0

SVDDT SVDON

R

R/W

0

∗

3

0

∗

3

SVDDT

SVDON

–

∗

2

–

∗

2

0

0

Low

On

Normal

Off

Unused

Unused

SVD evaluation data

SVD circuit On/Off

FF04H

SVDS3 SVDS2 SVDS1 SVDS0

R/W

SVDS3

SVDS2

SVDS1

SVDS0

0

0

0

0

SVD criteria voltage setting

0

2.20/1.05

8

2.60

1

2.20

9

2.70

2

2.20

10

2.80

3

2.20

11

2.90

4

2.20

12

3.00

5

2.30

13

3.10

6

2.40

14

3.20

7

2.50

15

3.30

[SVDS3–0]

Voltage(V)

[SVDS3–0]

Voltage(V)

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read

SVDS3–SVDS0: SVD criteria voltage setting register (FF04H)

Criteria voltage for SVD is set as shown in Table 4.13.3.1.

At initial reset, this register is set to "0".

SVDON: SVD control (ON/OFF) register (FF05H•D0)

Turns the SVD circuit ON and OFF.

When "1" is written: SVD circuit ON

When "0" is written: SVD circuit OFF

Reading: Valid

When the SVDON register is set to "1", a source voltage detection is executed by the SVD circuit. As soon

as SVDON is reset to "0", the result is loaded to the SVDDT latch. To obtain a stable detection result, the

SVD circuit must be ON for at least l00 µsec.

At initial reset, this register is set to "0".

SVDDT: SVD data (FF05H•D1)

This is the result of supply voltage detection.

When "0" is read: Supply voltage (V

DD

–V

SS

)

≥

Criteria voltage

When "1" is read: Supply voltage (V

DD

–V

SS

) < Criteria voltage

Writing: Invalid

The result of supply voltage detection at time of SVDON is set to "0" can be read from this latch.

At initial reset, SVDDT is set to "0".