9 i/o memory of serial interface – Epson S1C63558 User Manual

Page 102

92

EPSON

S1C63558 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Serial Interface)

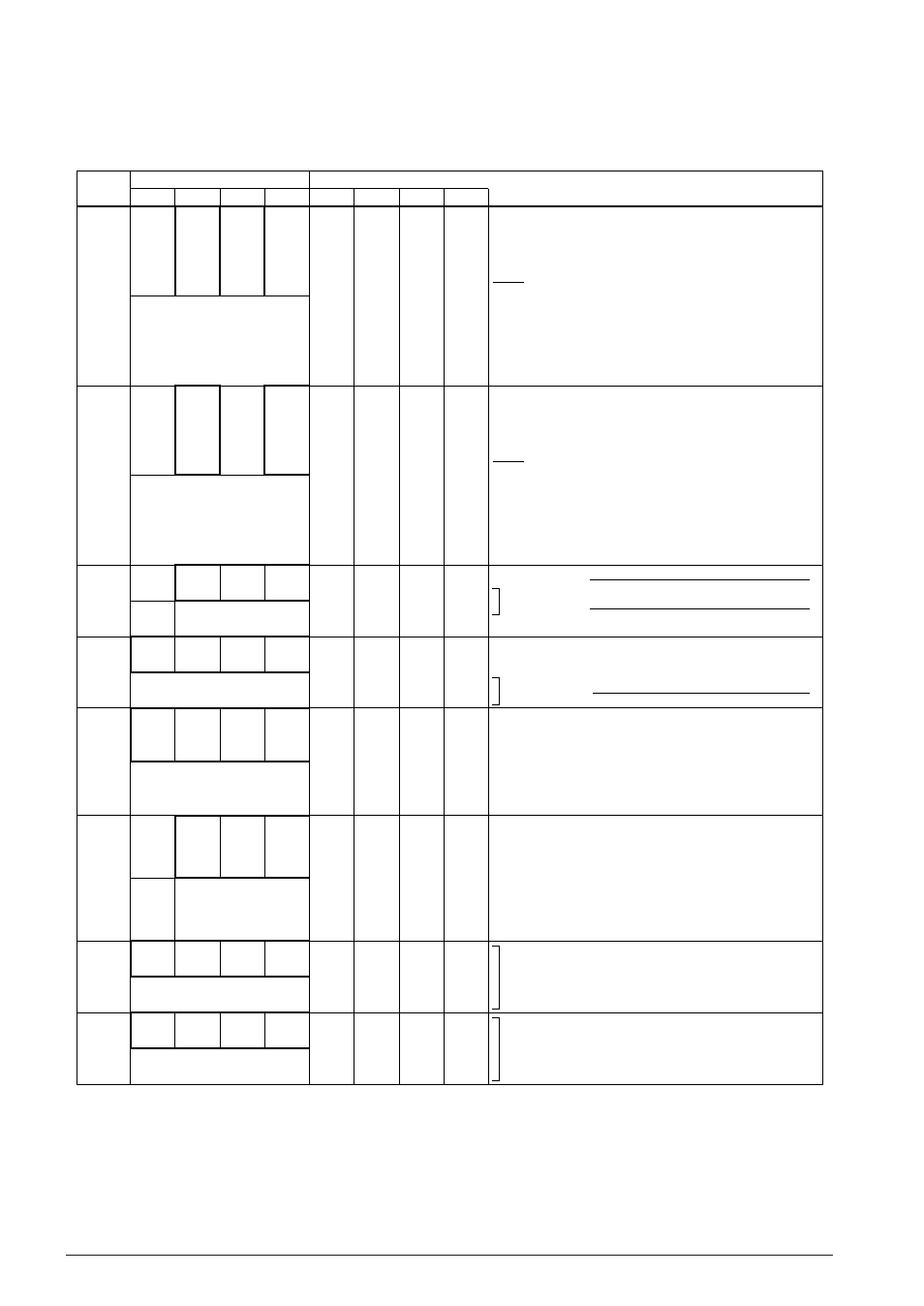

4.11.9 I/O memory of serial interface

Tables 4.11.9.1(a) and (b) show the serial interface control bits and their addresses.

Table 4.11.9.1(a) Serial interface control bits

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FF45H

PUL13

PUL12

PUL11

PUL10

R/W

PUL13

PUL12

PUL11

PUL10

1

1

1

1

On

On

On

On

Off

Off

Off

Off

P13 pull-up control register

General-purpose register when SIF (clock sync. slave) is selected

P12 pull-up control register

General-purpose register when SIF (clock sync. master) is selected

SCLK (I) pull-up control register

when SIF (clock sync. slave) is selected

P11 pull-up control register (ESIF=0)

General-purpose register when SIF is selected

P10 pull-up control register (ESIF=0)

SIN pull-up control register when SIF is selected

FF4DH

PUL33

PUL32

PUL31

PUL30

R/W

PUL33

PUL32

PUL31

PUL30

1

1

1

1

On

On

On

On

Off

Off

Off

Off

P33 pull-up control register

General-purpose register when SIF (clock sync. slave) is selected

P32 pull-up control register

General-purpose register when SIF (clock sync. master) is selected

SCLK (I) pull-up control register

when SIF (clock sync. slave) is selected

P31 pull-up control register (ESIFS=0)

General-purpose register when SIF is selected

P30 pull-up control register (ESIFS=0)

SIN pull-up control register when SIF is selected

0

Clk-sync. master

2

Async. 7-bit

1

Clk-sync. slave

3

Async. 8-bit

[SMD1S, 0S]

Mode

[SMD1S, 0S]

Mode

FF58H

0

SMD1S SMD0S

ESIFS

R

R/W

0

∗

3

SMD1S

SMD0S

ESIFS

–

∗

2

0

0

0

SIF

I/O

Unused

Serial I/F (2)

mode selection

Serial I/F (2) enable (P3x port function selection)

0

1200bps

1

600bps

2

2400bps

3

PT

[SCS1S, 0S]

Mode

FF59H

R/W

0

0

0

0

Enable

Odd

Disable

Even

Serial I/F (2) parity enable register

Serial I/F (2) parity mode selection

SIF (2) clock

source selection

R/W

FF5AH

0

0

0

0

Run

Trigger

Enable

Run

Trigger

Enable

Stop

–

Disable

Stop

–

Disable

Serial I/F (2) receive status (reading)

Serial I/F (2) receive trigger (writing)

Serial I/F (2) receive enable

Serial I/F (2) transmit status (reading)

Serial I/F (2) transmit trigger (writing)

Serial I/F (2) transmit enable

R

R/W

FF5BH

–

∗

2

0

0

0

Error

Reset

Error

Reset

Error

Reset

No error

–

No error

–

No error

–

Unused

Serial I/F (2) framing error flag status (reading)

Serial I/F (2) framing error flag reset (writing)

Serial I/F (2) parity error flag status (reading)

Serial I/F (2) parity error flag reset (writing)

Serial I/F (2) overrun error flag status (reading)

Serial I/F (2) overrun error flag reset (writing)

R/W

FF5CH

–

∗

2

–

∗

2

–

∗

2

–

∗

2

High

High

High

High

Low

Low

Low

Low

Serial I/F (2) t

ransmit/receive data

(low-order 4 bits)

LSB

R/W

FF5DH

–

∗

2

–

∗

2

–

∗

2

–

∗

2

High

High

High

High

Low

Low

Low

Low

MSB

Serial I/F (2) t

ransmit/receive data

(high-order 4 bits)

EPRS

PMDS

SCS1S SCS0S

EPRS

PMDS

SCS1S

SCS0S

RXTRGS RXENS TXTRGS TXENS

RXTRGS

RXENS

TXTRGS

TXENS

0

FERS

PERS

OERS

0

∗

3

FERS

PERS

OERS

TRXD3S TRXD2S TRXD1S TRXD0S

TRXD3S

TRXD2S

TRXD1S

TRXD0S

TRXD7S TRXD6S TRXD5S TRXD4S

TRXD7S

TRXD6S

TRXD5S

TRXD4S

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read