1) selection of port function, Table 4.6.6.1(b) control bits of i/o ports – Epson S1C63558 User Manual

Page 55

S1C63558 TECHNICAL MANUAL

EPSON

45

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (I/O Ports)

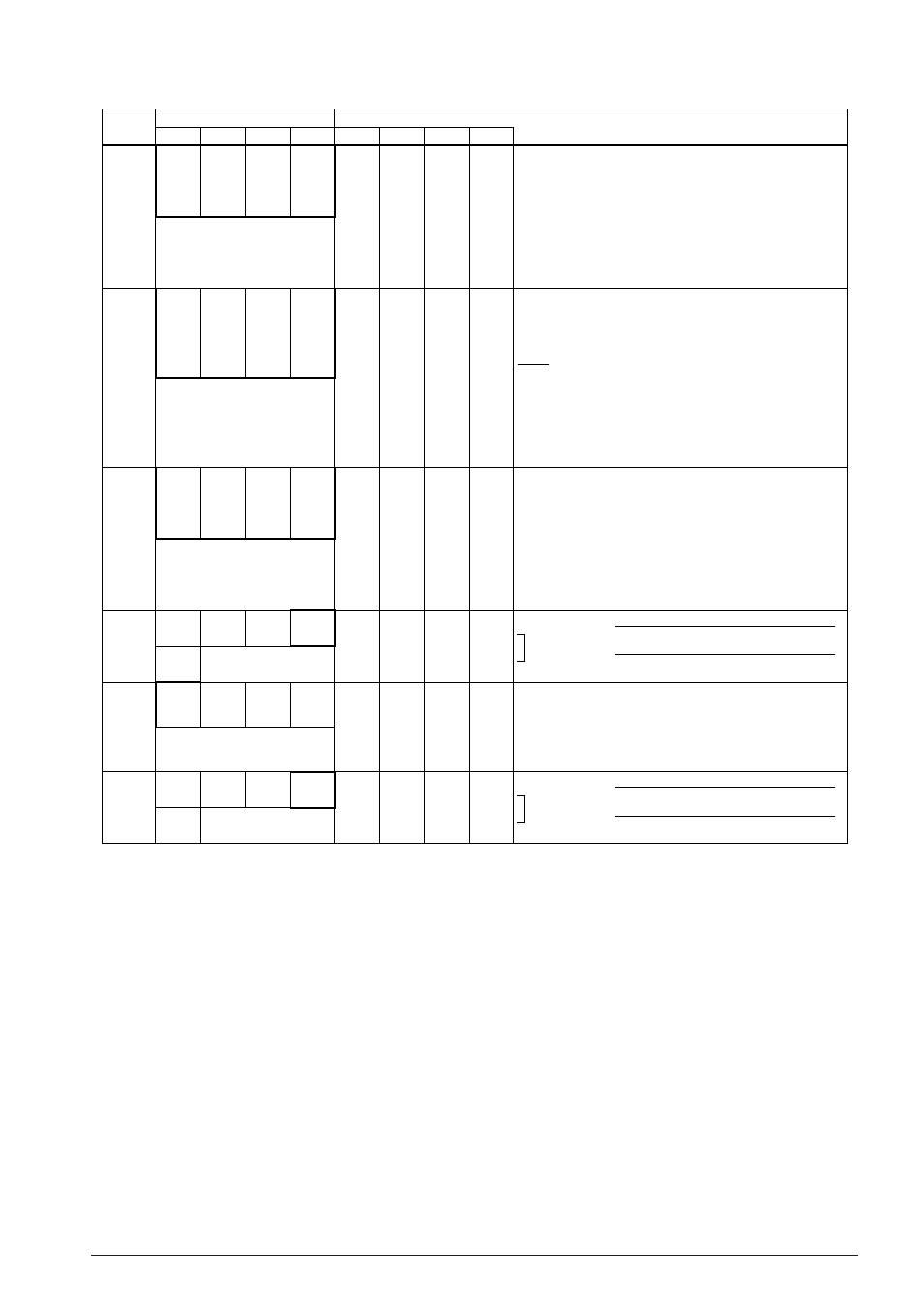

Table 4.6.6.1(b) Control bits of I/O ports

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

FF61H

EXLCDC ALOFF

ALON

LPAGE

R/W

EXLCDC

ALOFF

ALON

LPAGE

0

1

0

0

Enable

All Off

All On

F100-F15F

Disable

Normal

Normal

F000-F05F

Expanded LCD driver signal control

LCD all Off control

LCD all On control

Display memory area selection (when 1/8 duty is selected)

General-purpose register when 1/16, 1/17 duty is selected

0

Clk-sync. master

2

Async. 7-bit

1

Clk-sync. slave

3

Async. 8-bit

[SMD1, 0]

Mode

[SMD1, 0]

Mode

FF70H

0

SMD1

SMD0

ESIF

R

R/W

0

∗

3

SMD1

SMD0

ESIF

–

∗

2

0

0

0

SIF

I/O

Unused

Serial I/F (1)

mode selection

Serial I/F (1) enable (P1x port function selection)

0

Clk-sync. master

2

Async. 7-bit

1

Clk-sync. slave

3

Async. 8-bit

[SMD1S, 0S]

Mode

[SMD1S, 0S]

Mode

FF58H

0

SMD1S SMD0S

ESIFS

R

R/W

0

∗

3

SMD1S

SMD0S

ESIFS

–

∗

2

0

0

0

SIF

I/O

Unused

Serial I/F (2)

mode selection

Serial I/F (2) enable (P3x port function selection)

FF4CH

IOC33

IOC32

IOC31

IOC30

R/W

IOC33

IOC32

IOC31

IOC30

0

0

0

0

Output

Output

Output

Output

Input

Input

Input

Input

P33 I/O control register

General-purpose register when SIF (clock sync. slave) is selected

P32 I/O control register

General-purpose register when SIF (clock sync.) is selected

P31 I/O control register (ESIFS=0)

General-purpose register when SIF is selected

P30 I/O control register (ESIFS=0)

General-purpose register when SIF is selected

FF4DH

PUL33

PUL32

PUL31

PUL30

R/W

PUL33

PUL32

PUL31

PUL30

1

1

1

1

On

On

On

On

Off

Off

Off

Off

P33 pull-up control register

General-purpose register when SIF (clock sync. slave) is selected

P32 pull-up control register

General-purpose register when SIF (clock sync. master) is selected

SCLK (I) pull-up control register

when SIF (clock sync. slave) is selected

P31 pull-up control register (ESIFS=0)

General-purpose register when SIF is selected

P30 pull-up control register (ESIFS=0)

SIN pull-up control register when SIF is selected

FF4EH

R/W

P33

P32

P31

P30

–

∗

2

–

∗

2

–

∗

2

–

∗

2

High

High

High

High

Low

Low

Low

Low

P33 I/O port data

General-purpose register when SIF (clock sync. slave) is selected

P32 I/O port data

General-purpose register when SIF (clock sync.) is selected

P31 I/O port data (ESIFS=0)

General-purpose register when SIF is selected

P30 I/O port data (ESIFS=0)

General-purpose register when SIF is selected

P33

(XSRDYS)

P32

(XSCLKS)

P31

(SOUTS)

P30

(SINS)

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read

(1) Selection of port function

EXLCDC: Expanded LCD driver signal control register (FF61H•D3)

Sets P22 and P23 to the CL signal and the FR signal output ports.

When "1" is written: CL/FR signal output

When "0" is written: I/O port

Reading: Valid

When setting P22 to the CL (LCD synchronous signal) output and P23 to the FR (LCD frame signal)

output, write "1" to this register and when they are used as I/O ports, write "0".

The CL and FR signals are output from the P22 terminal and P23 terminal immediately after the functions

are switched by the EXLCDC register. In this case, the control registers for P22 and P23 can be used as

general purpose registers that do not affect the output.

At initial reset, this register is set to "0".