Code space management – Wavetronix Click 500 (programmable controller) (CLK-500) - Developer Guide User Manual

Page 107

106

CHAPTER 10 • MEMORY MANAGEMENT

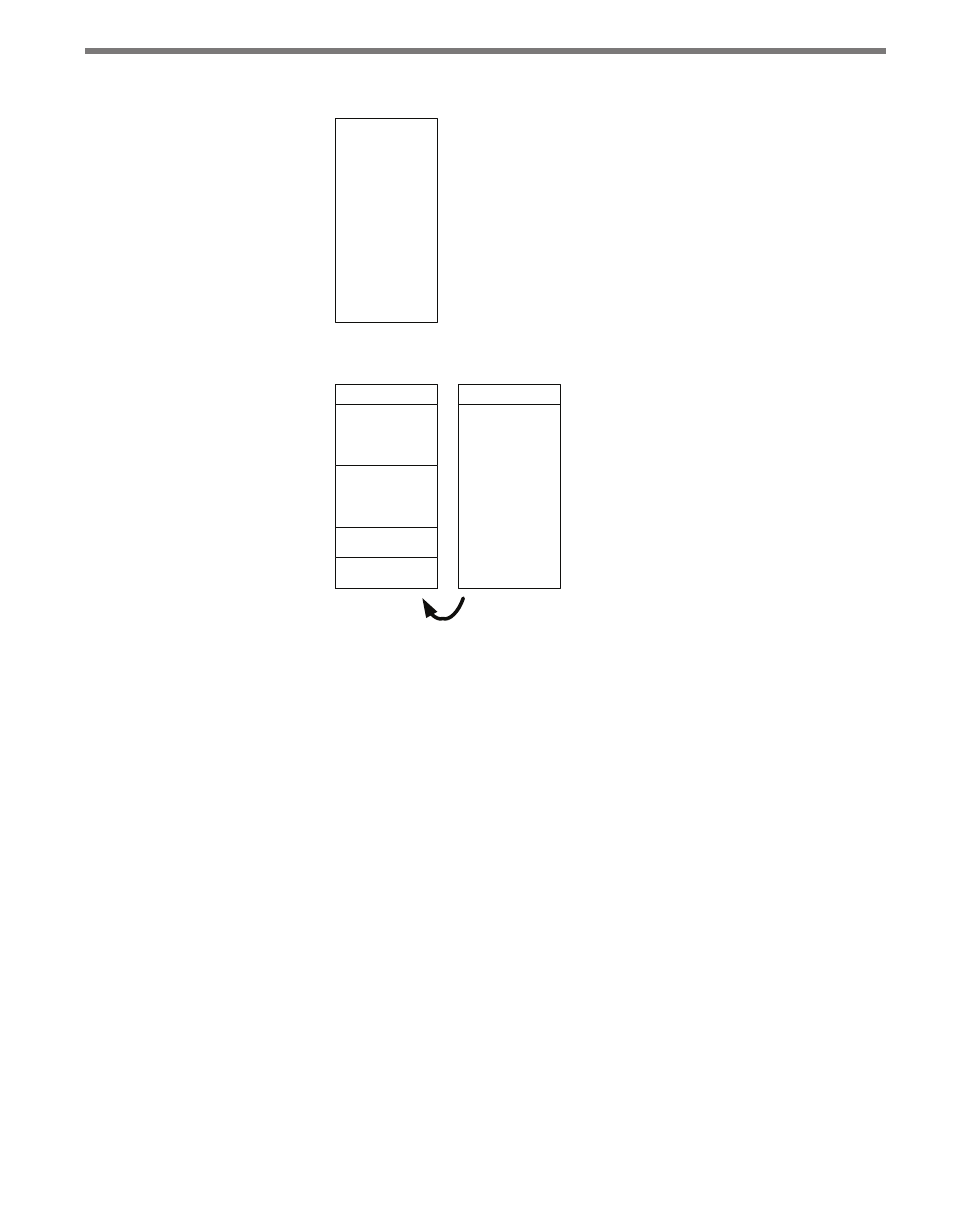

512K Fast

SRAM

Code Image &

Flash Data

512K Flash

0x00 0000

Far Data

512K SRAM

0x01 0000

Root Code

0x07 FFFF

0x10 0000

User Block

Root Data

0x17 FFFF

Far Code

0x05 0000

Far Data

0x07 8000

0x02 0000

User Block

Copy on boot-up

Figure 10.1 – Simplified Overview of Memory Map

The Click 500 implements a feature that enables separate instruction and data space in or-

der to provide 128 K of fast access memory. By default, fast access instructions are stored in

the root code block (first 64 K) and fast access data is stored in the root data block (second

64 K). Additional instructions are stored in the far code block (192 K starting at hex address

0x02 0000); additional volatile data is stored in the far data blocks on both SRAM chips

(about 692 K in total). Non-volatile data is stored in the 32 K user block.

While the main program executes, the Fast-execution SRAM is addressed from 0x00 0000

to 0x07 FFFF, and the second 512 K of SRAM is addressed from 0x01 0000 to 0x17 FFFF.

Code Space Management

The Dynamic C compiler automatically places any code that does not fit in the root code

block into the far code block. Altogether, there is about 256 K of memory for code, which

should be sufficient for many applications. If you are running short on code space, there is a

compiler setting that allows you to optimize compilation for space. To view code space us-

age and where specific routines have been placed, open the .org and .map files (see Figures

10.2 and 10.3).