10 firmware building blocks, 1 introduction, 2 clock synthesizer – Sundance SMT381 2004 User Manual

Page 70

10 Firmware Building Blocks

10.1 Introduction

This section explains some of the basic low level firmware blocks that come with the

example firmware design of the SMT381-VP.

10.2 Clock Synthesizer

A three wire uni-directional control interface is implemented between the FPGA of the

SMT338-VP and the clock synthesizer present on the SMT381.

One 16 bit register in the SMT338-VP firmware is used for the setup of the clock

synthesizer. The data word needed for the setup of the synthesizer is only 14 bits

long - thus the 16 bit register is sufficient to receive data from the ComPort in one

write cycle from the Host. When the ComPort receives the data for the clock

synthesizer register it configures the internal firmware register accordingly and

asserts the enable pin on the Clock Synthesizer State Machine.

The Clock Synthesizer State Machine generates the handshaking signals to clock

data into the synthesizer. The synthesizer then generates an output clock depending

on the setup given by the user. The output of the Synthesizer is a LVPECL signal.

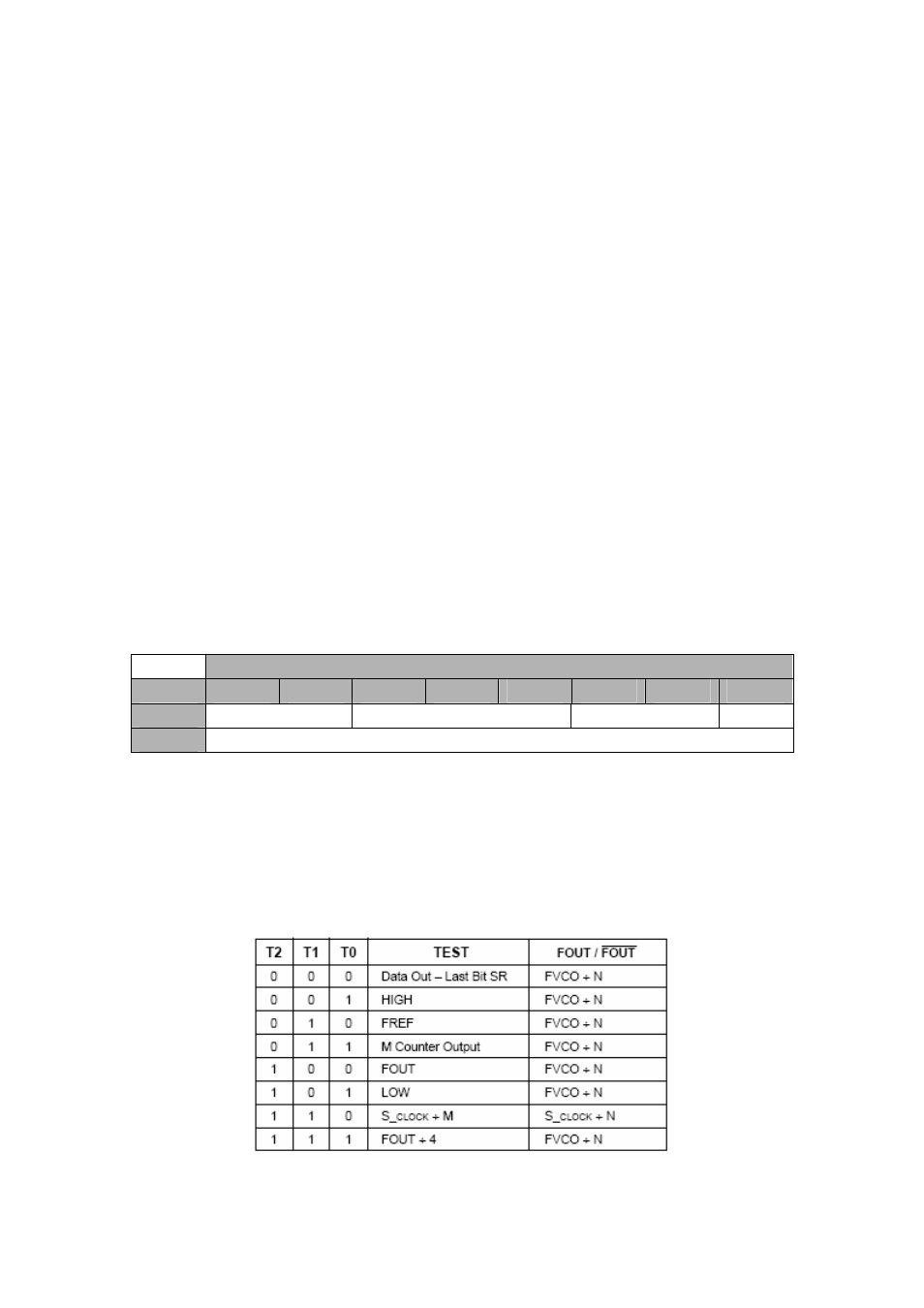

The Clock Synthesizer register (present on the SMT338-VP firmware side) is used

for the setup of the clock synthesizer on the SMT381. The table below shows the

setup of this register:

Clock Control Register

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Do Not Care

Test Bits

Output Division

M Count

0

M Count

Figure 61. Clock Synthesizer Register.

As the ComPort bit-stream is 16 bits long both bytes are written simultaneously. The

most significant byte (Byte 1) contains the test bits, output division bits and one M

count bit. The test bits selects between various internal node values and is controlled

by the T[2:0] bits in the serial data stream (This feature is can be set up by the

FPGA, but the value of the Test output is not read by the FPGA). The node values

are shown in the table below.

Table 12. Clock Synthesizer Test Output.