4 firmware description, 1 main states – Sundance SMT381 2004 User Manual

Page 39

4 Firmware Description

4.1 Main States

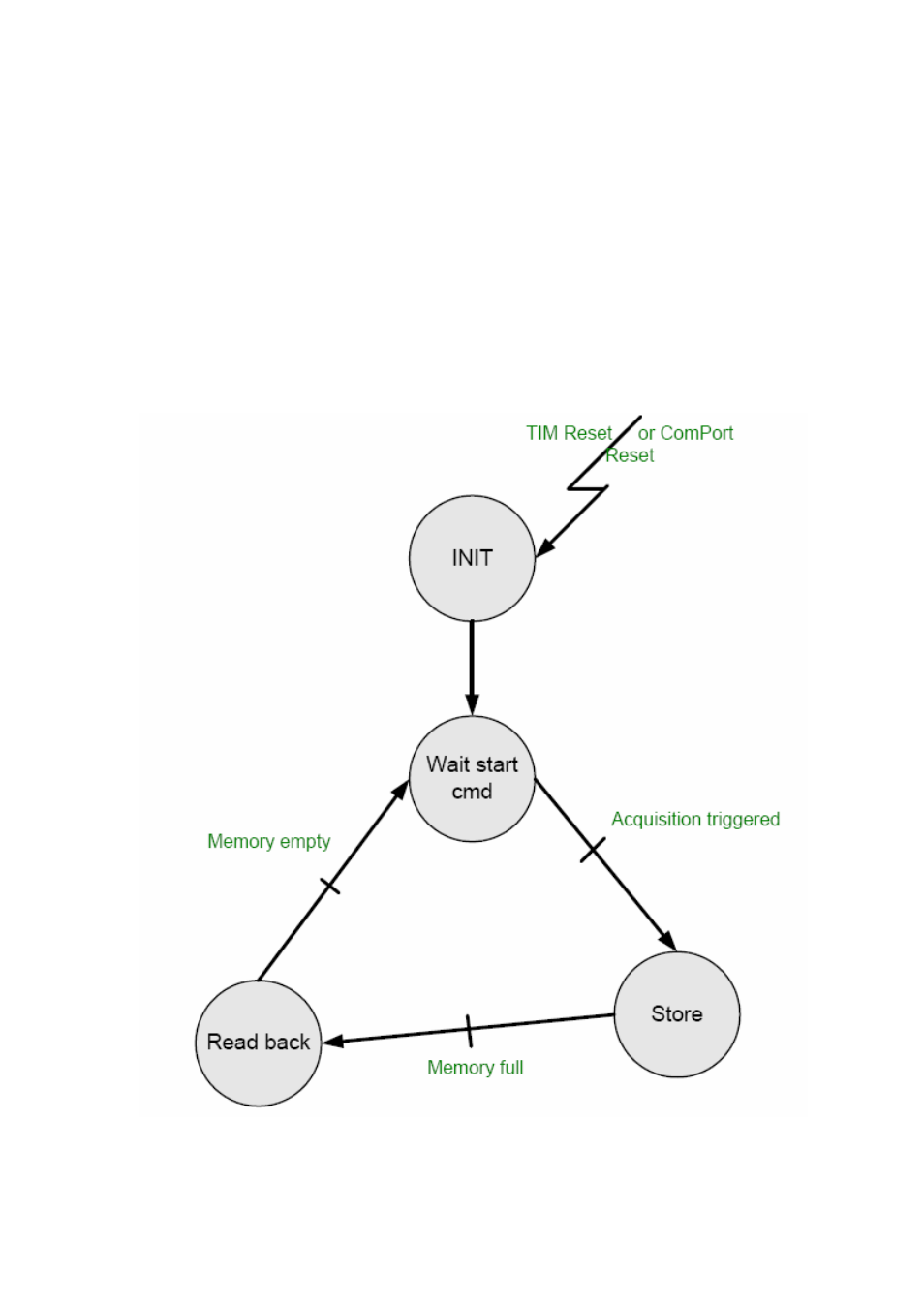

At reset, the FPGA is in the INIT state where internal memory and registers are reset.

It then waits for data from the SHB interface to write to the DDR memory (state

“STORE”). Once the memory is full, upon a trigger, data is read back and written to

the DAC (state “READ BACK”). When the whole memory has been read back the

FPGA can carry on cycling through the memory, or go back into the “WAIT START

CMD” state and wait for a new data from the SHB interface. The following diagram

describes the sequence of events during an acquisition:

Figure 21. SMT381-VP Firmware State Diagram.

This manual is related to the following products: