Read response format – Sundance SMT381 2004 User Manual

Page 47

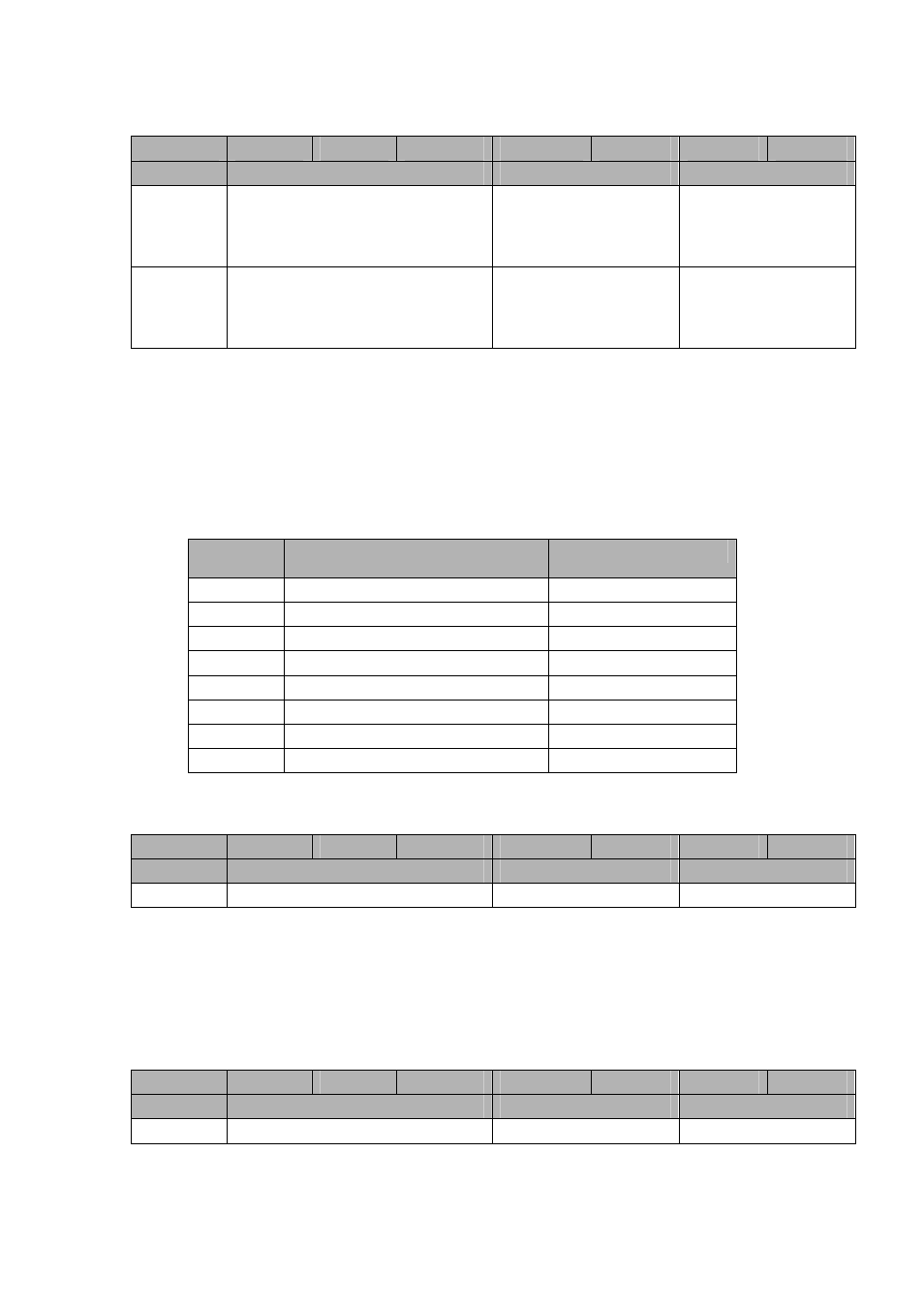

Read Response Format:

31 .. 28

27 .. 24

23 .. 20

19 .. 16

15 .. 12

11 .. 8

7 .. 4

3 .. 0

Command

Address

Data MSB

Data LSB

0x2

0x2

0x2

0x2

0x022

0x023

0x024

0x025

SMT338-VP Serial No

SMT338-VP Serial No

SMT338-VP Serial No

SMT338-VP Serial No

Byte A

Byte B

Byte C

Byte D

0x2

0x2

0x2

0x2

0x02A

0x02B

0x02C

0x02D

SMT381 Serial No

SMT381 Serial No

SMT381 Serial No

SMT381 Serial No

Byte A

Byte B

Byte C

Byte D

Figure 29. Serial Number Registers Cont. (Read Only).

5.4.5 DAC Clock Source Registers (Write Add 0x801)

The A and B channels of the DAC can receive a clock from the on-board VCO, the

on-board clock synthesizer, or from an external clock (RF or ECL). The following

table shows the different combinations for setting up the SMT381 clock tree.

Register

Value

A Channel Clock Source

B Channel Clock Source

0x0000

On-board VCO

On-board VCO

0x0001

On-board Clock Synthesizer

On-board Clock Synthesizer

0x0002

External ECL Clock

External ECL Clock

0x0003

External ECL Clock

External ECL Clock

0x0004

On-board VCO

On-board VCO

0x0005

On-board Clock Synthesizer

On-board Clock Synthesizer

0x0006

External RF Clock

External RF Clock

0x0007

External RF Clock

External RF Clock

Figure 30. Clock Source Selection Table (Write Only).

31 .. 28

27 .. 24

23 .. 20

19 .. 16

15 .. 12

11 .. 8

7 .. 4

3 .. 0

Command

Address

Data MSB

Data LSB

0x1

0x801

0x00

Clock Register Value

Figure 31. Clock Source Register (Write Only).

5.4.6 Clock Synthesizer Setup Register (Write Add 0x800)

This register sets up the frequency of the clock synthesizer on the SMT381. Any

write operation to this register will trigger the clock synthesizer interface control logic

to initialize the clock synthesizer with its new value.

31 .. 28

27 .. 24

23 .. 20

19 .. 16

15 .. 12

11 .. 8

7 .. 4

3 .. 0

Command

Address

Data MSB

Data LSB

0x1

0x800

Data

Data

Figure 32. Clock Synthesizer Setup Register (Write Only).