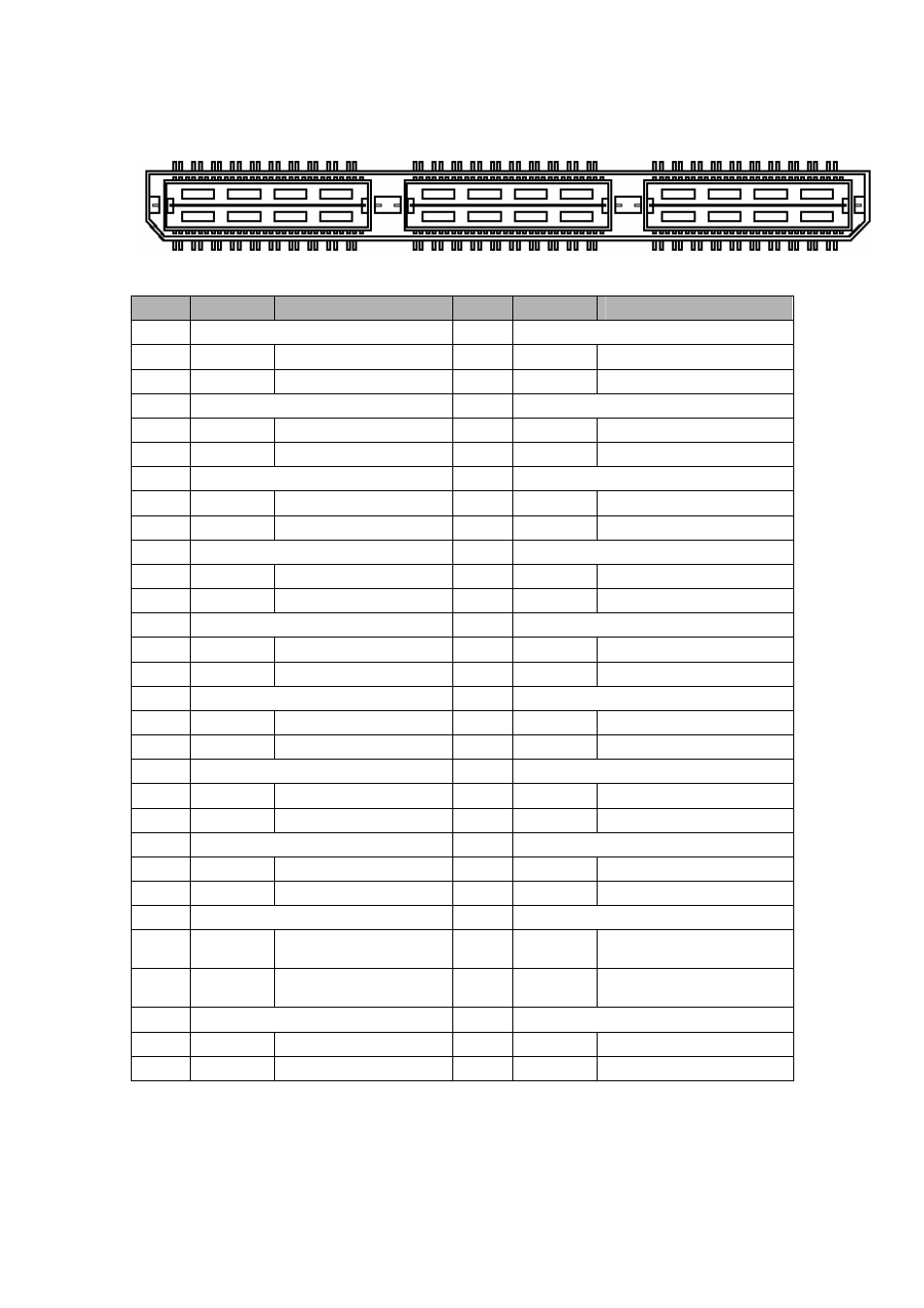

Bank a bank b bank c, Bank a – Sundance SMT381 2004 User Manual

Page 30

Bank A

Bank B

Bank C

1 3 5 7

41 43

81 83

2 4 6 8

Bank A

Pin No

Pin Name

Signal Description

Pin No

Pin Name

Signal Description

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

1

DOAI0p

Data In 0 Channel A, pos.

2

DOBI0p

Data In 1 Channel A, pos.

3

DOAI0n

Data In 0 Channel A, neg.

4

DOBI0n

Data In 1 Channel A, neg.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

5

DOAI1p

Data In 2 Channel A, pos.

6

DOBI1p

Data In 3 Channel A, pos.

7

DOAI1n

Data In 2 Channel A, neg.

8

DOBI1n

Data In 3 Channel A, neg.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

9

DOAI2p

Data In 4 Channel A, pos.

10

DOBI2p

Data In 5 Channel A, pos.

11

DOAI2n

Data In 4 Channel A, neg.

12

DOBI2n

Data In 5 Channel A, neg.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

13

DOAI3p

Data In 6 Channel A, pos.

14

DOBI3p

Data In 7 Channel A, pos.

15

DOAI3n

Data In 6 Channel A, neg.

16

DOBI3n

Data In 7 Channel A, neg.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

17

DOAI4p

Data In 8 Channel A, pos.

18

DOBI4p

Data In 9 Channel A, pos.

19

DOAI4n

Data In 8 Channel A, neg.

20

DOBI4n

Data In 9 Channel A, neg.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

21

DOAI5p

Data In 10 Channel A, pos.

22

DOBI5p

Data In 11 Channel A, pos.

23

DOAI5n

Data In 10 Channel A, neg.

24

DOBI5n

Data In 11 Channel A, neg.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

25

DOAI6p

Data In 12 Channel A, pos.

26

DOBI6p

Data In 13 Channel A, pos.

27

DOAI6n

Data In 12 Channel A, neg.

28

DOBI6n

Data In 13 Channel A, neg.

Dir

Reserved

Dir

Reserved

29

Reserved

Reserved

30

Reserved

Reserved

31

Reserved

Reserved

32

Reserved

Reserved

Dir

Daughter Card to Main Module

Dir

Main Module to Daughter Card

33

ClkOIp

Output Ready, I channel,

pos

34

DOIRIp

Loop back clock to DAC, pos.

35

ClkOIn

Output Ready, I channel,

neg

36

DOIRIn

Loop back clock to DAC, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

37

SysClockp

System clock, pos.

38

ExtTriggerIp

External Trigger A, pos.

39

SysClockn

System clock, neg.

40

ExtTriggerIn

External Trigger A, neg.

Figure 11. Daughter Card Interface: Data Signals Connector and Pinout (Bank A).