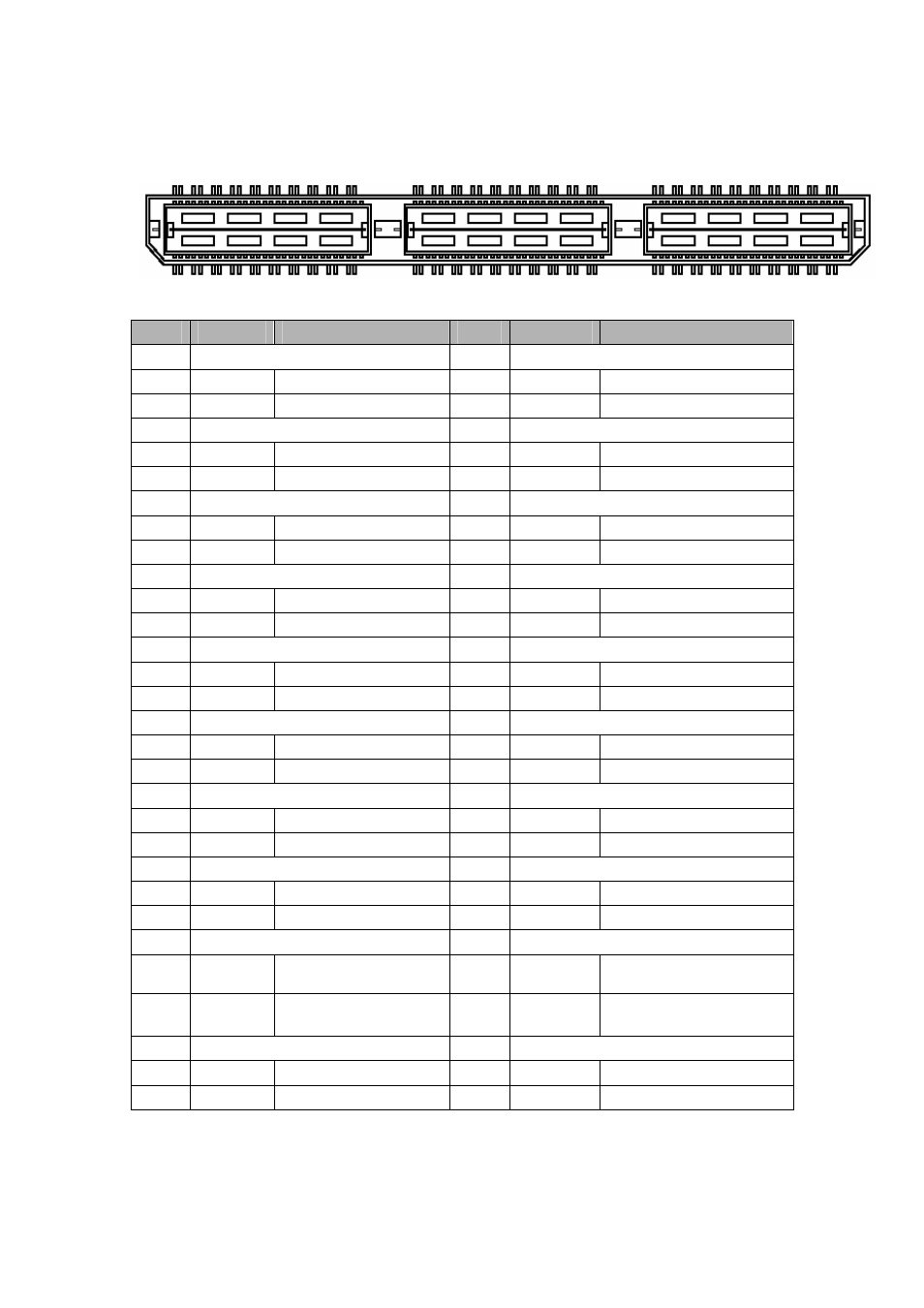

Bank a bank b bank c, Bank c – Sundance SMT381 2004 User Manual

Page 32

Bank A

Bank B

Bank C

1 3 5 7

41 43

81 83

2 4 6 8

Bank C

Pin No

Pin Name

Signal Description

Pin No

Pin Name

Signal Description

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

81

DOAQ0p

Data In 0 Channel B, pos.

82

DOBQ0p

Data In 1 Channel B, pos.

83

DOAQ0n

Data In 0 Channel B, neg.

84

DOBQ0n

Data In 1 Channel B, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

85

DOAQ1p

Data In 2 Channel B, pos.

86

DOBQ1p

Data In 3 Channel B, pos.

87

DOAQ1n

Data In 2 Channel B, neg.

88

DOBQ1n

Data In 3 Channel B, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

89

DOAQ2p

Data In 4 Channel B, pos.

90

DOBQ2p

Data In 5 Channel B, pos.

91

DOAQ2n

Data In 4 Channel B, neg.

92

DOBQ2n

Data In 5 Channel B, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

93

DOAQ3p

Data In 6 Channel B, pos.

94

DOBQ3p

Data In 7 Channel B, pos.

95

DOAQ3n

Data In 6 Channel B, neg.

96

DOBQ3n

Data In 7 Channel B, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

97

DOAQ4p

Data In 8 Channel B, pos.

98

DOBQ4p

Data In 9 Channel B, pos.

99

DOAQ4n

Data In 8 Channel B, neg.

100

DOBQ4n

Data In 9 Channel B, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

101

DOAQ5p

Data In 10 Channel B, pos.

102

DOBQ5p

Data In 11 Channel B, pos.

103

DOAQ5n

Data In 10 Channel B, neg.

104

DOBQ5n

Data In 11 Channel B, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

105

DOAQ6p

Data In 12 Channel B, pos.

106

DOBQ6p

Data In 13 Channel B, pos.

107

DOAQ6n

Data In 12 Channel B, neg.

108

DOBQ6n

Data In 13 Channel B, neg.

Dir

Reserved

Dir

Reserved

109

Reserved

Reserved

110

Reserved

Reserved

111

Reserved

Reserved

112

Reserved

Reserved

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

113

ClkOQp

Output Ready, Q channel,

pos

114

DOIRQp

Loop back clock to FPGA, pos.

115

ClkOQn

Output Ready, Q channel,

neg

116

DOIRQn

Loop back clock to FPGA, neg.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

117

RslClockp

Rsl Clock, pos.

118

ExtTriggerQp

External Trigger A, pos.

119

RslClockn

Rsl Clock, neg.

120

ExtTriggerQn

External Trigger A, neg.

Figure 13. Daughter Card Interface: Data Signals Connector and Pinout (Bank C).