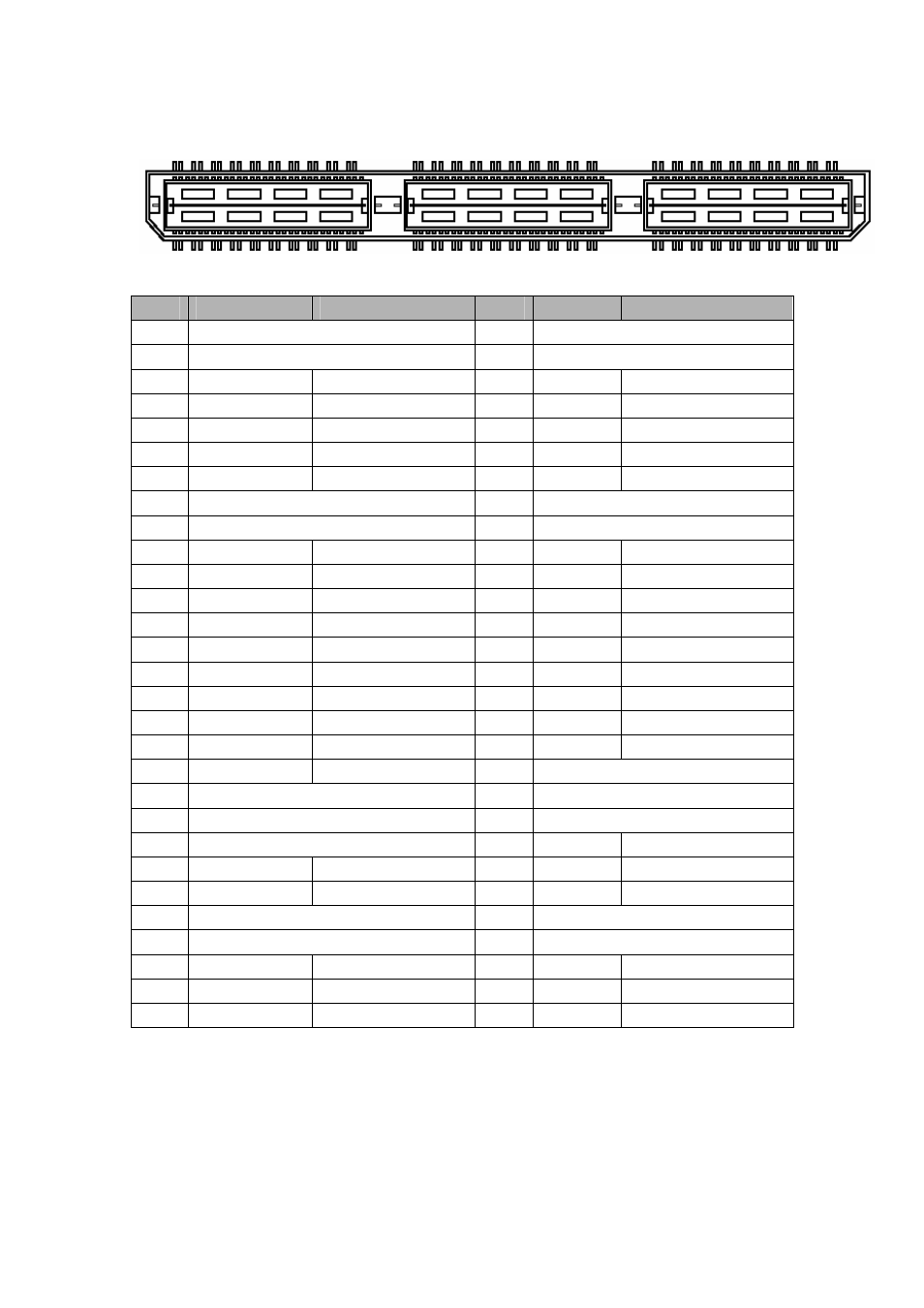

Bank a bank b bank c, Bank b – Sundance SMT381 2004 User Manual

Page 31

Bank A

Bank B

Bank C

1 3 5 7

41 43

81 83

2 4 6 8

Bank B

Pin No

Pin Name

Signal Description

Pin No

Pin Name

Signal Description

Type

MSP system signals

Type

MSP system signals

Dir

Bi-Directional

Dir

Bi-Directional

41

SMBClk

TmpCntrl0

42

SMBData

TmpCntrl1

43

SMBnAlert

TmpCntrl2

44

SerialNo

Serial Number

45

Reserved

Reserved

46

Reserved

Reserved

47

Reserved

Reserved

48

Reserved

Reserved

49

D3V3Enable

D3V3Enable

50

D1V8Enable

D1V8Enable

Type

FPGA system signals

Type

FPGA system signals

Dir

Bi-Directional

Dir

Bi-Directional

51

DACCntrl0

DAC Control 0

52

DACCntrl0

DAC Control 1

53

DACCntrl0

DAC Control 2

54

DACCntrl0

DAC Control 3

55

DACCntrl0

DAC Control 4

56

AdjClkSClk

AdjClockCntrl0

57

AdjClkSData

AdjClockCntrl1

58

AdjClkSLoad

AdjClockCntrl2

59

AdjClkTest

AdjClockCntrl3

60

PllClk

PllCntrl0

61

PllData

PllCntrl1

62

PllLe

PllCntrl2

63

PllFoLd

PllCntrl3

64

AdcAClkSel

AdcAClkSel

65

AdcBClkSel

AdcBClkSel

66

IntClkDivEn

IntClkDivEnable

67

IntClkDivnReset

IntClkDivnReset

68

IntExtClkSel

IntExtClkSel

69

IntExtClkSelnReset

IntExtClkSelnReset

Type

FPGA JTAG

Type

FPGA JTAG

Dir

Bi-Directional

Dir

Bi-Directional

70

FpgaVref

FpgaVref

71

FpgaTck

FpgaTck

72

FpgaTms

FpgaTms

73

FpgaTdi

FpgaTdi

74

FpgaTdo

FpgaTdo

Type

MSP JTAG

Type

MSP JTAG

Dir

Bi-Directional

Dir

Bi-Directional

75

MspVref

MspVref

76

MspTck

MspTck

77

MspTms

MspTms

78

MspTdi

MspTdi

79

MspTdo

MspTdo

80

MspnTrst

MspnTrst

Figure 12. Daughter Card Interface: Data Signals Connector and Pinout (Bank B).