2 power-on values et1100, Power-on values et1100, Et1100 – BECKHOFF EtherCAT Registers Section II User Manual

Page 89

ESC specific registers (0x0E00:0x0EFF)

Slave Controller

– Register Description

II-77

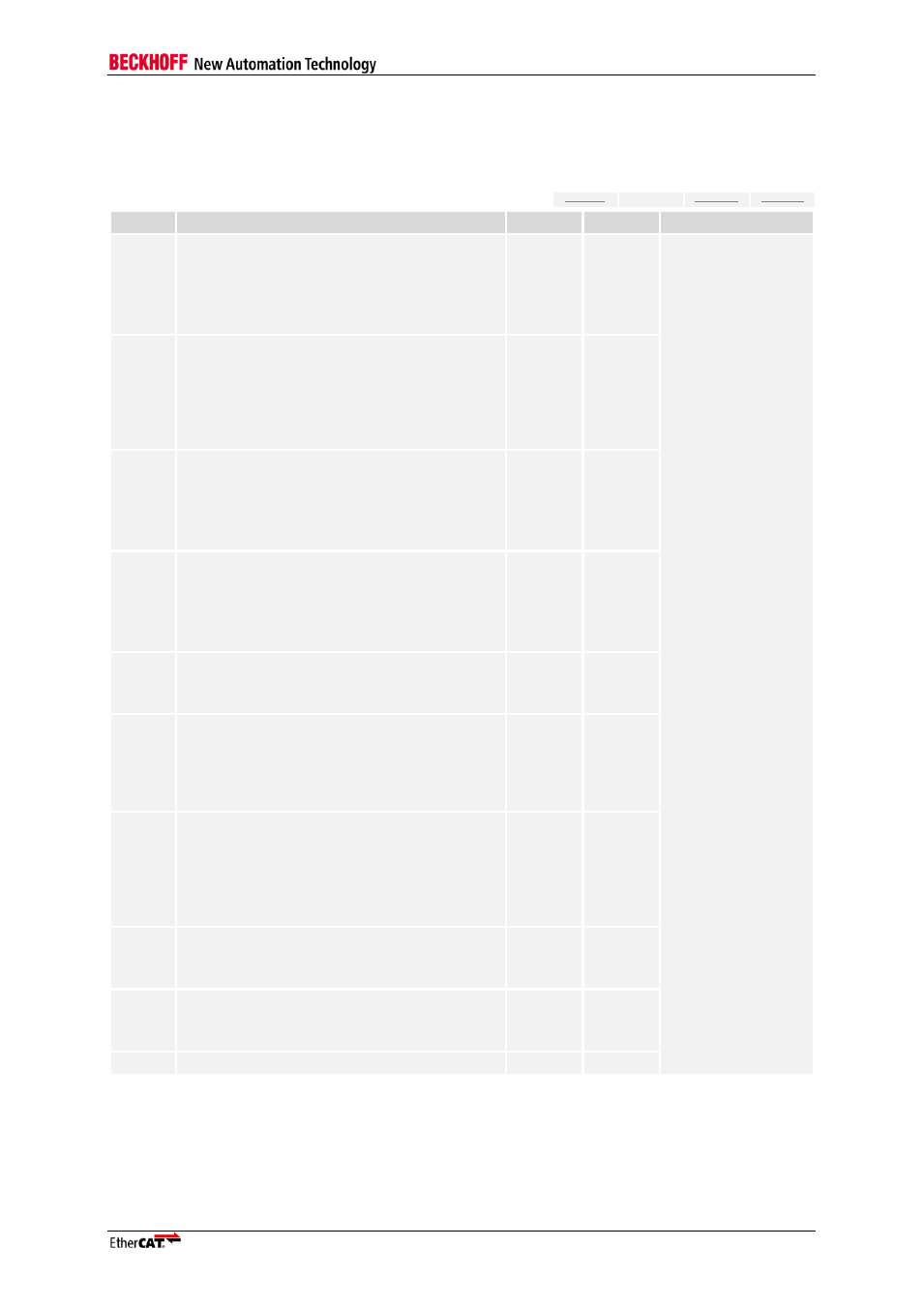

3.50.2 Power-On Values ET1100

Table 131: Register Power-On Values ET1100 (0x0E00:0x0E01)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

1:0

Port mode (P_MODE):

00: Logical ports 0 and 1 available

01: Logical ports 0, 1 and 2 available

10: Logical ports 0, 1 and 3 available

11: Logical ports 0, 1, 2 and 3 available

r/-

r/-

Depends on Hardware

configuration

5:2

Physical layer of available ports (P_CONF).

Bit 2

→ logical port 0, Bit 3 → logical port 1,

Bit 4

→ third logical port (2/3), Bit 5 → logical

port 3.

0:

EBUS

1:

MII

r/-

r/-

7:6

CPU clock output (CLK_MODE):

00: Off

– PDI[7] available as PDI port

01: PDI[7] = 25MHz

10: PDI[7] = 20MHz

11: PDI[7] = 10MHz

r/-

r/-

9:8

TX signal shift (C25_SHI):

00: MII TX signals shifted by 0°

01: MII TX signals shifted by 90°

10: MII TX signals shifted by 180°

11: MII TX signals shifted by 270°

r/-

r/-

10

CLK25 Output Enable (C25_ENA):

0:

Disabled

– PDI[31] available as PDI port

1:

Enabled

– PDI[31] = 25MHz (OSC)

r/-

r/-

11

Transparent Mode MII (Trans_Mode_Ena):

0:

Disabled

1:

Enabled

– ERR is input (0: TX signals

are tristated, 1: ESC is driving TX

signals)

r/-

r/-

12

Digital Control/State Move

(Ctrl_Status_Move):

0:

Control/Status signals are mapped to

PDI[39:32]

– if available

1:

Control/Status signals are remapped to

the highest available PDI Byte.

r/-

r/-

13

PHY Address Offset (PHYAD_OFF):

0:

No PHY address offset

1:

PHY address offset is 16

r/-

r/-

14

PHY Link Polarity (LINKPOL):

0:

LINK_MII is active low

1:

LINK_MII is active high

r/-

r/-

15

Reserved configuration bit

r/-

r/-