4 sync out unit, Sync out unit, Table 110: register activation register (0x0981) – BECKHOFF EtherCAT Registers Section II User Manual

Page 80: 0x0981, Activation, 0x0982:0x0983, Pulse length of syncsignals

Distributed Clocks (0x0900:0x09FF)

II-68

Slave Controller

– Register Description

3.49.4 SYNC Out Unit

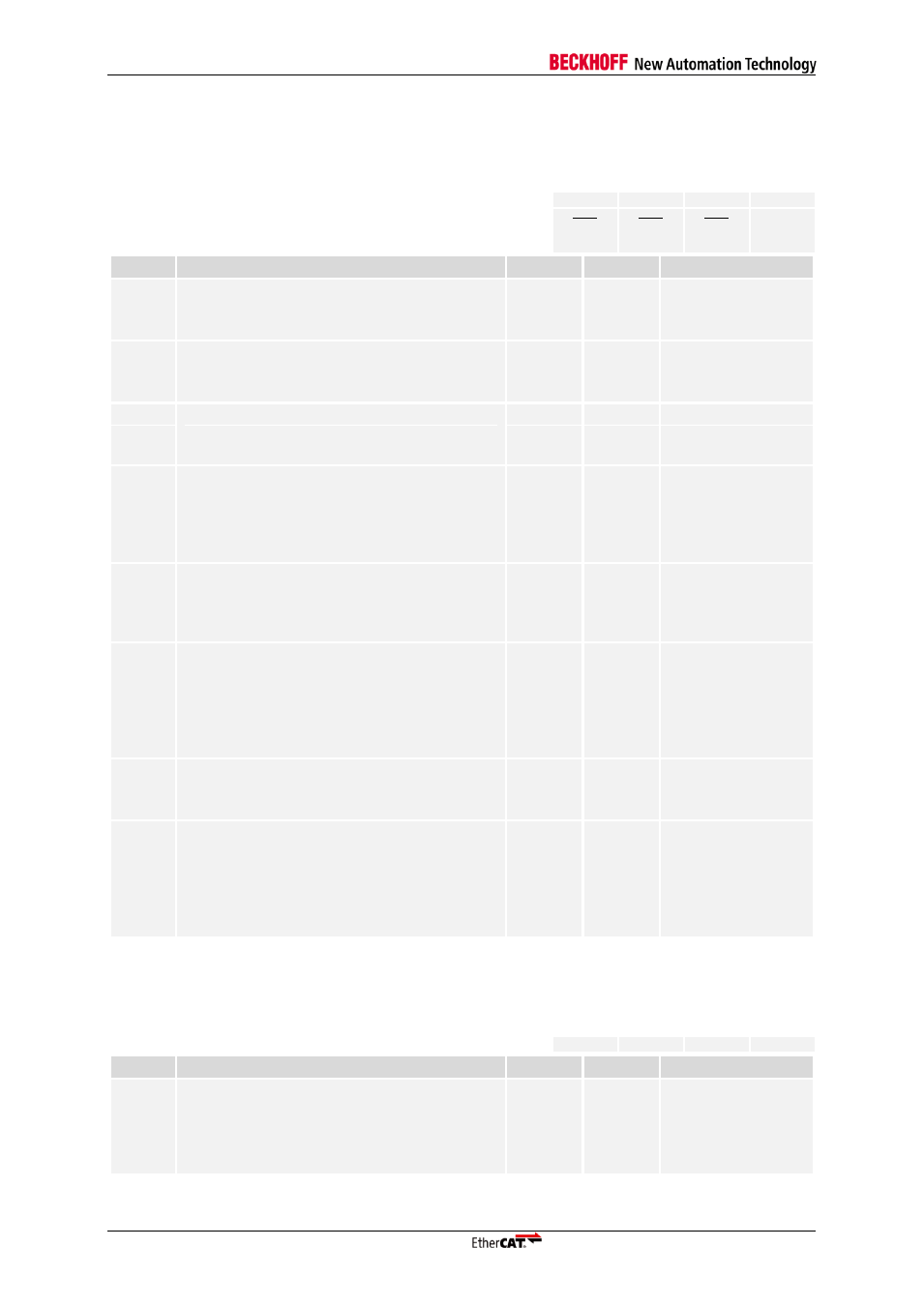

Table 110: Register Activation register (0x0981)

ESC20

ET1100

ET1200

IP Core

[7:3]

[7:3]

[7:3]

[7:3]

V2.2.0/

V2.02a

Bit

Description

ECAT

PDI

Reset Value

0

Sync Out Unit activation:

0:

Deactivated

1: Activated

r/(w)

r/(w)

0

1

SYNC0 generation:

0:

Deactivated

1:

SYNC0 pulse is generated

r/(w)

r/(w)

0

2

SYNC1 generation:

0:

Deactivated

1:

SYNC1 pulse is generated

r/(w)

r/(w)

0

3

Auto-activation by writing Start Time Cyclic

Operation (0x0990:0x0997):

0:

Disabled

1:

Auto-activation enabled. 0x0981.0 is set

automatically after Start Time is written.

r/(w)

r/(w)

0

4

Extension of Start Time Cyclic Operation

(0x0990:0x0993):

0:

No extension

1:

Extend 32 bit written Start Time to 64 bit

r/(w)

r/(w)

0

5

Start Time plausibility check:

0:

Disabled. SyncSignal generation if Start

Time is reached.

1:

Immediate SyncSignal generation if

Start Time is outside near future (see

0x0981.6)

r/(w)

r/(w)

0

6

Near future configuration (approx.):

0:

½ DC width future (2

31

ns or 2

63

ns)

1: ~2.1 sec. future (2

31

ns)

r/(w)

r/(w)

0

7

SyncSignal debug pulse (Vasily bit):

0:

Deactivated

1:

Immediately generate one ping only on

SYNC0-1 according to 0x0981[2:1] for

debugging

This bit is self-clearing, always read 0.

r/(w)

r/(w)

0

NOTE: Write to this register depends upon setting of 0x0980.0.

Table 111: Register Pulse Length of SyncSignals (0x0982:0x983)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

15:0

Pulse length of SyncSignals (in Units of

10ns)

0:

Acknowledge mode: SyncSignal will be

cleared by reading SYNC[1:0] Status

register

r/-

r/-

IP Core: Depends on

configuration

Others: 0, later

EEPROM ADR 0x0002