0x0517, Mii management pdi access state, 0x0518:0x051b – BECKHOFF EtherCAT Registers Section II User Manual

Page 65: Phy port status

MII Management Interface (0x0510:0x0515)

Slave Controller

– Register Description

II-53

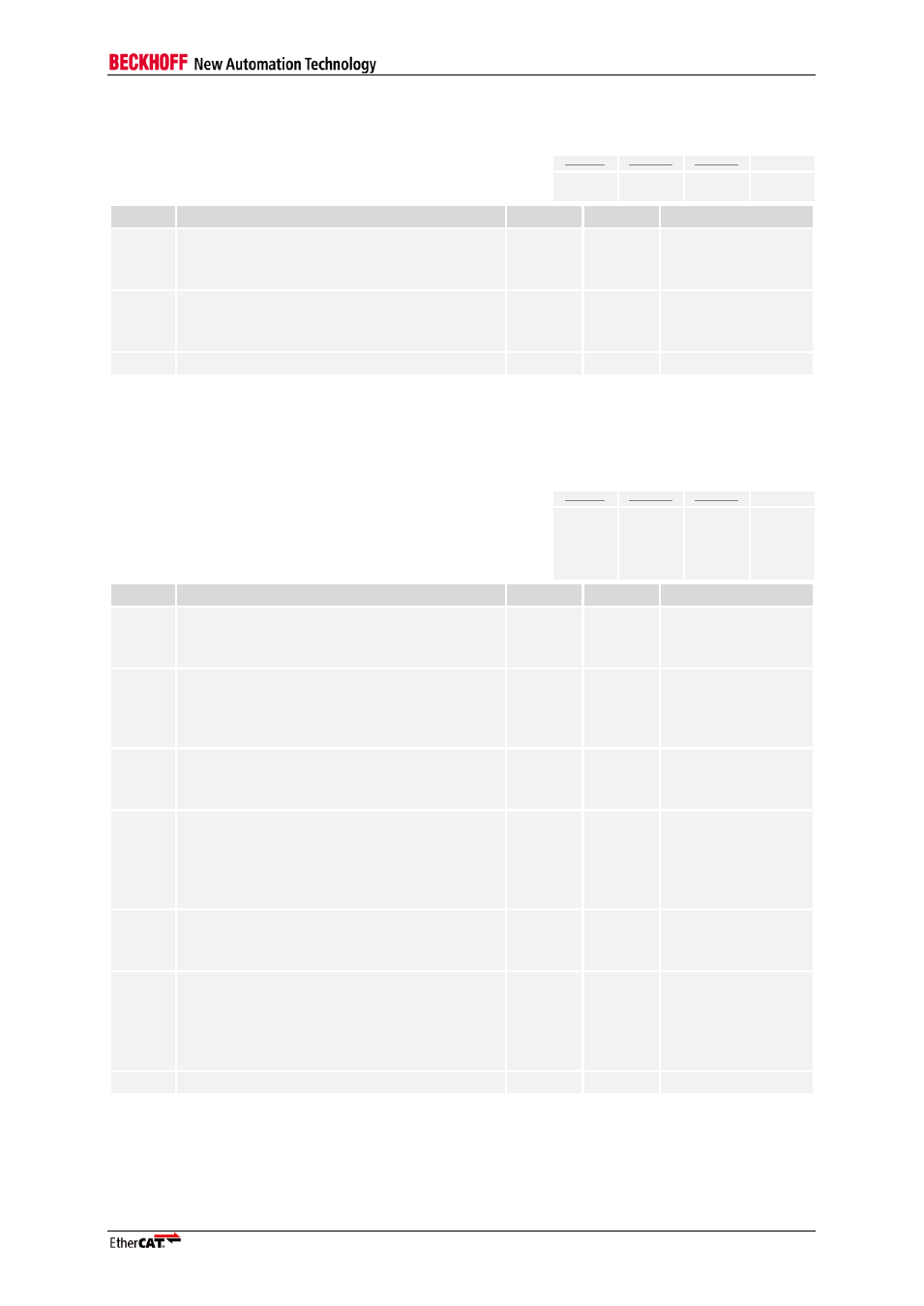

Table 76: Register MII Management PDI Access State (0x0517)

ESC20

ET1100

ET1200

IP Core

V2.0.0/

V2.00a

Bit

Description

ECAT

PDI

Reset Value

0

Access to MII management:

0:

ECAT has access to MII management

1:

PDI has access to MII management

r/-

r/(w)

0

1

Force PDI Access State:

0:

Do not change Bit 517.0

1:

Reset Bit 517.0 to 0

r/w

r/-

0

7:2

Reserved, write 0

r/-

r/-

0

NOTE: r/ (w): assigning access to PDI (bit 0 = 1) is only possible if 0x0516.0=0 and 0x0517.1=0, and if the SII

EEPROM is loaded (0x0110[0]=1).

Table 77: Register PHY Port y (port number y=0 to 3) Status (0x0518+y)

ESC20

ET1100

ET1200

IP Core

V2.0.0/

V2.00a;

[5]

V2.0.2/

V2.02a

Bit

Description

ECAT

PDI

Reset Value

0

Physical link status (PHY status register 1.2):

0:

No physical link

1:

Physical link detected

r/-

r/-

0

1

Link status (100 Mbit/s, Full Duplex,

Autonegotiation):

0:

No link

1:

Link detected

r/-

r/-

0

2

Link status error:

0:

No error

1:

Link error, link inhibited

r/-

r/-

0

3

Read error:

0:

No read error occurred

1:

A read error has occurred

Cleared by writing any value to at least one

of the PHY Status Port y registers.

r/(w/clr)

r/(w/clr)

0

4

Link partner error:

0:

No error detected

1:

Link partner error

r/-

r/-

0

5

PHY configuration updated:

0:

No update

1:

PHY configuration was updated

Cleared by writing any value to at least one

of the PHY Status Port y registers.

r/(w/clr)

r/(w/clr)

0

7:6

Reserved

r/-

r/-

0

NOTE: r/ (w): write access depends on assignment of MI (ECAT/PDI).