0x0510:0x0511, Mii management control/status – BECKHOFF EtherCAT Registers Section II User Manual

Page 63

MII Management Interface (0x0510:0x0515)

Slave Controller

– Register Description

II-51

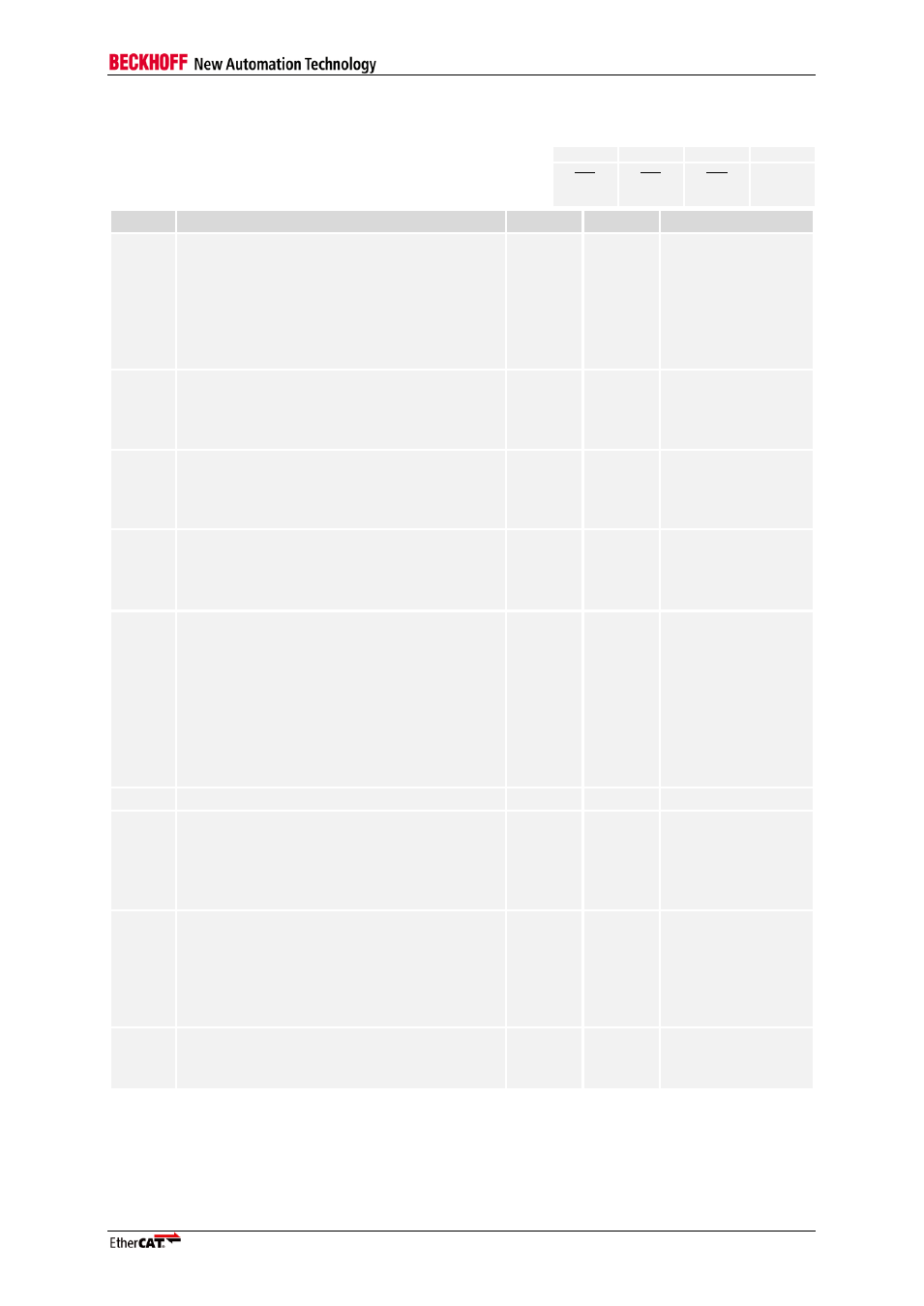

Table 71: Register MII Management Control/Status (0x0510:0x0511)

ESC20

ET1100

ET1200

IP Core

[13]

[13]

[13]

[13]

V2.0.0/

V2.00a

Bit

Description

ECAT

PDI

Reset Value

0

Write enable*:

0:

Write disabled

1:

Write enabled

This bit is always 1 if PDI has MI control.

ET1100-0000/-0001 exception:

Bit is not always 1 if PDI has MI control, and

bit is writable by PDI.

r/(w)

r/-

0

1

Management Interface can be controlled by

PDI (registers 0x0516-0 x0517):

0:

Only ECAT control

1:

PDI control possible

r/-

r/-

IP Core since

V2.0.0/V2.00a: 1

Others: 0

2

MI link detection (link configuration, link

detection, registers 0x0518-0x051B):

0:

Not available

1:

MI link detection active

r/-

r/-

IP Core: Depends on

configuration

Others: 0

7:3

PHY address of port 0

IP Core V3.0.0/3.00c:

PHY address of port 0-3 depending on

0x0512[7].

r/-

r/-

ET1100, ET1200:

PHYAD_OFF for bit 7

IP Core: Depends on

configuration

Others: 0

9:8

Command register*

:

Write: Initiate command.

Read: Currently executed command

Commands:

00: No command/MI idle (clear error bits)

01: Read

10: Write

Others: Reserved/invalid commands (do not

issue)

r/(w)

r/(w)

0

12:10

Reserved, write 0

r/-

r/-

0

13

Read error:

0:

No read error

1:

Read error occurred (PHY or register

not available)

Cleared by writing to this register.

r/(w)

r/(w)

0

14

Command error:

0:

Last Command was successful

1:

Invalid command or write command

without Write Enable

Cleared with a valid command or by writing

“00” to Command register bits [9:8].

r/-

r/-

0

15

Busy:

0:

MI control state machine is idle

1:

MI control state machine is active

r/-

r/-

0

NOTE: r/ (w): write access depends on assignment of MI (ECAT/PDI). Write access is generally blocked if

Management interface is busy (0x0510.15=1).

* Write enable bit 0 is self-clearing at the SOF of the next frame (or at the end of the PDI access), Command bits

[9:8] are self-clear

ing after the command is executed (Busy ends). Writing “00” to the command register will also

clear the error bits [14:13]. The Command bits are cleared after the command is executed.