BECKHOFF EtherCAT Registers Section II User Manual

Page 29

ESC DL Control (0x0100:0x0103)

Slave Controller

– Register Description

II-17

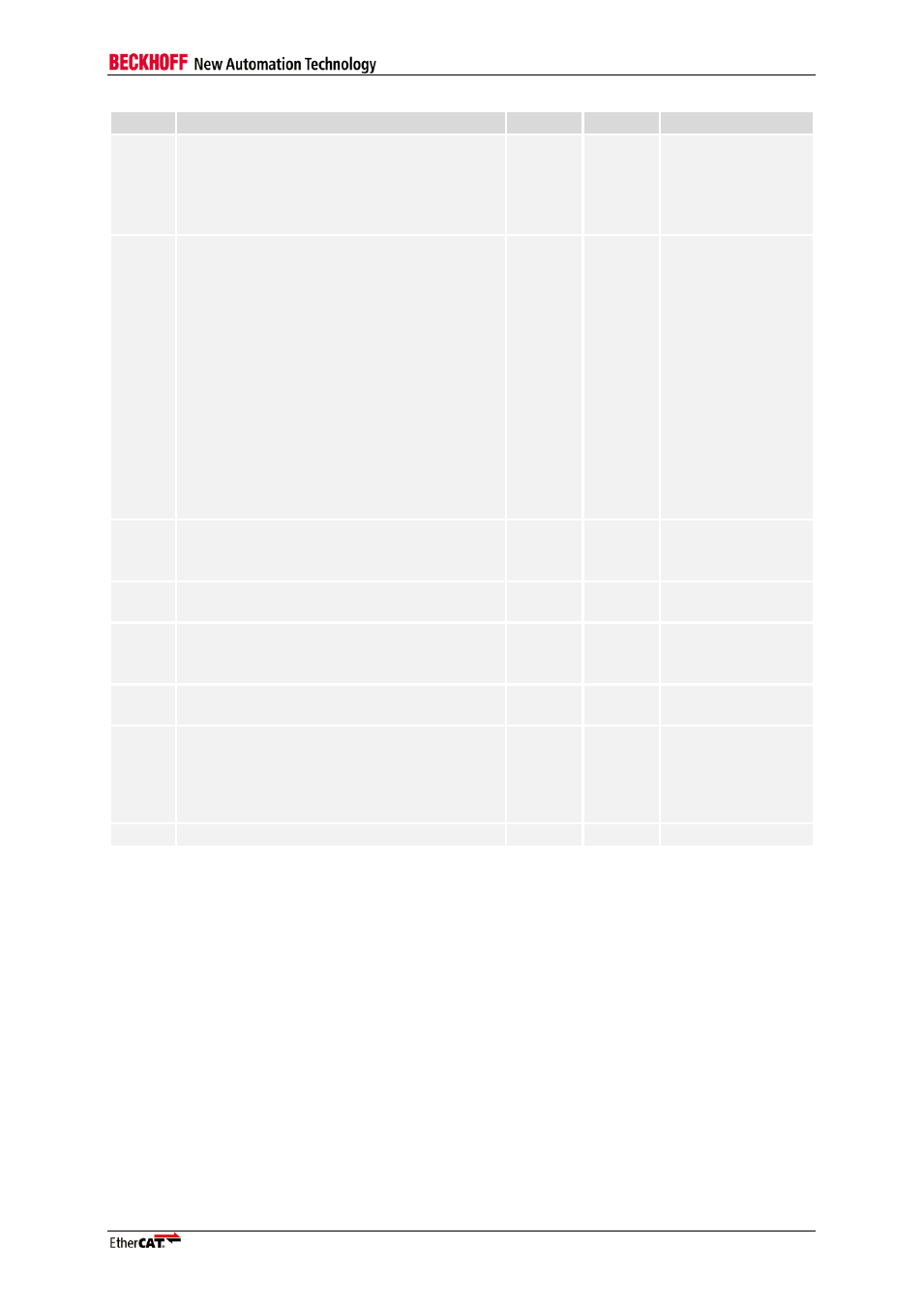

Bit

Description

ECAT

PDI

Reset Value

15:14

Loop Port 3:

00: Auto

01: Auto Close

10: Open

11: Closed

r/w*

r/-

ET1200: 11

others: 00

18:16

RX FIFO Size (ESC delays start of

forwarding until FIFO is at least half full).

RX FIFO Size/RX delay reduction** :

Value: EBUS:

MII:

0:

-50 ns

-40 ns (-80 ns***)

1:

-40 ns

-40 ns (-80 ns***)

2:

-30 ns

-40 ns

3:

-20 ns

-40 ns

4:

-10 ns

no change

5:

no change no change

6:

no change no change

7:

default

default

NOTE: EEPROM value is only taken over at first

EEPROM load after power-on or reset

r/w

r/-

7

IP Core since

V2.4.3/V2.04d:

7, later EEPROM

ADR 0x0005[11:9]

inverted

19

EBUS Low Jitter:

0:

Normal jitter

1:

Reduced jitter

r/w

r/-

0

21:20

Reserved, write 0

r/w

r/-

0, later EEPROM

ADR 0x0005[5:4]

22

EBUS remote link down signaling time:

0:

Default (~660 ms)

1:

Reduced (~80 µs)

r/w

r/-

0, later EEPROM

ADR 0x0005[6]

23

Reserved, write 0

r/w

r/-

0, later EEPROM

ADR 0x0005[7]

24

Station alias:

0:

Ignore Station Alias

1:

Alias can be used for all configured

address command types (FPRD,

FPWR, …)

r/w

r/-

0

31:25

Reserved, write 0

r/-

r/-

0

* Loop configuration changes are delayed until the end of a currently received or transmitted frame at the port.

** The possibility of RX FIFO Size reduction depends on the clock source accuracy of the ESC and of every

connected EtherCAT/Ethernet devices (master, slave, etc.). RX FIFO Size of 7 is sufficient for 100ppm accuracy,

FIFO Size 0 is possible with 25ppm accuracy (frame size of 1518/1522 Byte).

*** IP Core since V3.0.0/V3.00c only