26 esc configuration (0x0141), Esc configuration (0x0141), Table 30: register esc configuration (0x0141) – BECKHOFF EtherCAT Registers Section II User Manual

Page 37

ESC Configuration (0x0141)

Slave Controller

– Register Description

II-25

3.26 ESC Configuration (0x0141)

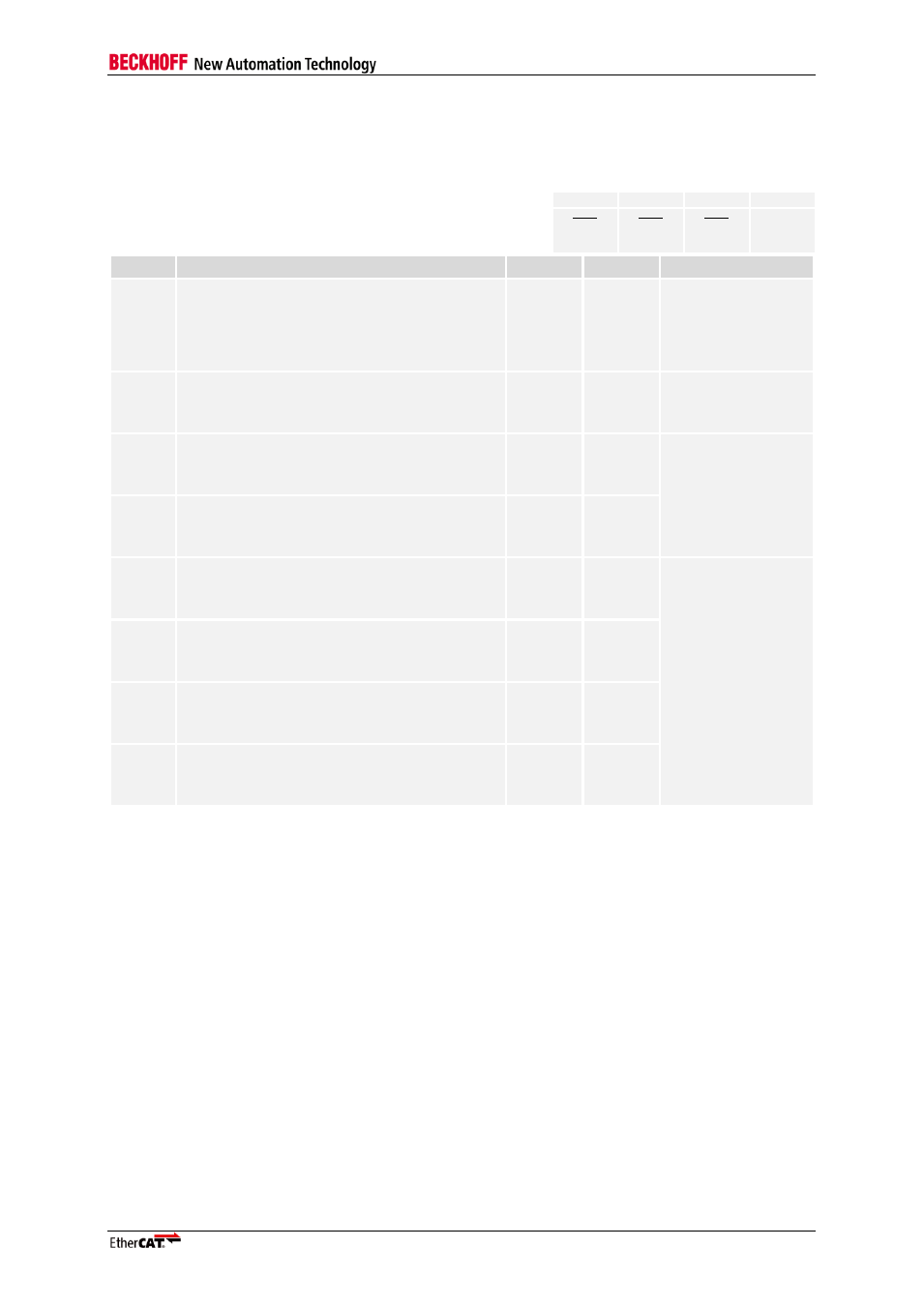

Table 30: Register ESC Configuration (0x0141)

ESC20

ET1100

ET1200

IP Core

[7:1]

[7:4]

[7:2]

[7:4]

V2.2.0/

V2.02a

Bit

Description

ECAT

PDI

Reset Value

0

Device emulation (control of AL status):

0:

AL status register has to be set by PDI

1:

AL status register will be set to value

written to AL control register

r/-

r/-

IP Core: 1 with Digital

I/O PDI,

PDI_EMULATION pin

with µC/On-chip bus

Others: 0, later

EEPROM ADR 0x0000

1

Enhanced Link detection all ports:

0:

disabled (if bits [7:4]=0)

1:

enabled at all ports (overrides bits [7:4])

r/-

r/-

0, later EEPROM ADR

0x0000

2

Distributed Clocks SYNC Out Unit:

0:

disabled (power saving)

1:

enabled

r/-

r/-

IP Core: Depends on

configuration

Others: 0, later

EEPROM ADR 0x0000

3

Distributed Clocks Latch In Unit:

0:

disabled (power saving)

1:

enabled

r/-

r/-

4

Enhanced Link port 0:

0:

disabled (if bit 1=0)

1:

enabled

r/-

r/-

0, later EEPROM ADR

0x0000

5

Enhanced Link port 1:

0:

disabled (if bit 1=0)

1:

enabled

r/-

r/-

6

Enhanced Link port 2:

0:

disabled (if bit 1=0)

1:

enabled

r/-

r/-

7

Enhanced Link port 3:

0:

disabled (if bit 1=0)

1:

enabled

r/-

r/-