1 pdi digital i/o configuration, Pdi digital i/o configuration, Digital i/o – BECKHOFF EtherCAT Registers Section II User Manual

Page 40: 0x0150

PDI Configuration (0x0150:0x0153)

II-28

Slave Controller

– Register Description

3.28.1 PDI Digital I/O configuration

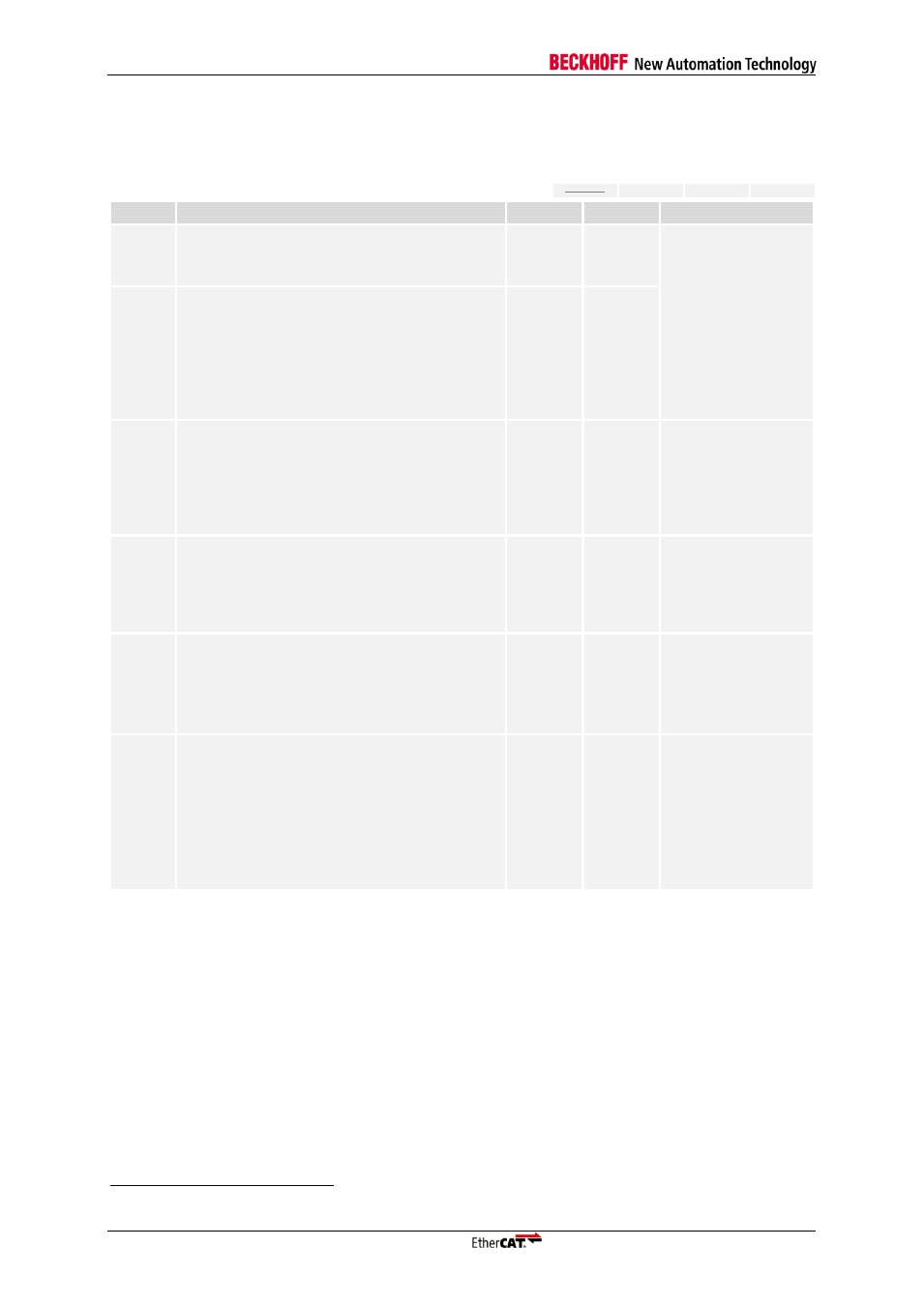

Table 33: Register PDI Digital I/O configuration (0x0150)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

0

OUTVALID polarity:

0:

Active high

1:

Active low

r/-

r/-

IP Core: 0

Others: 0, later

EEPROM ADR 0x0001

1

OUTVALID mode:

0:

Output event signaling

1:

Process Data Watchdog trigger

(WD_TRIG) signaling on OUTVALID pin

(see SyncManager). Output data is

updated if watchdog is triggered.

Overrides 0x0150[7:6]

r/-

r/-

2

Unidirectional/Bidirectional mode*:

0:

Unidirectional mode: input/output

direction of pins configured individually

1:

Bidirectional mode: all I/O pins are

bidirectional, direction configuration is

ignored

r/-

r/-

IP Core: 1

Others: 0, later

EEPROM ADR 0x0001

3

Watchdog behavior:

0:

Outputs are reset immediately after

watchdog expires

1:

Outputs are reset with next output event

that follows watchdog expiration

r/-

r/-

IP Core: 0

Others: 0, later

EEPROM ADR 0x0001

5:4

Input DATA is sampled at

00: Start of Frame

2

01: Rising edge of LATCH_IN

10: DC SYNC0 event

11: DC SYNC1 event

r/-

r/-

IP Core: Depends on

configuration

Others: 0, later

EEPROM ADR 0x0001

7:6

Output DATA is updated at

00: End of Frame

01: reserved

10: DC SYNC0 event

11: DC SYNC1 event

If 0x0150[1]=1, output DATA is updated at

Process Data Watchdog trigger event

(0x0150[7:6] are ignored)

r/-

r/-

IP Core: Depends on

configuration

Others: 0, later

EEPROM ADR 0x0001

* IP Core: I/O direction depends on configuration, bidirectional mode is not supported.

Table Register Sync/Latch[1:0] PDI Configuration (0x0151) moved to chapter 3.28.7

2

ET1200: LATCH_IN/SOF reflects Start of Frame (SOF) if input data is sampled with SOF or DC SYNC events.