BECKHOFF EtherCAT Registers Section II User Manual

Page 5

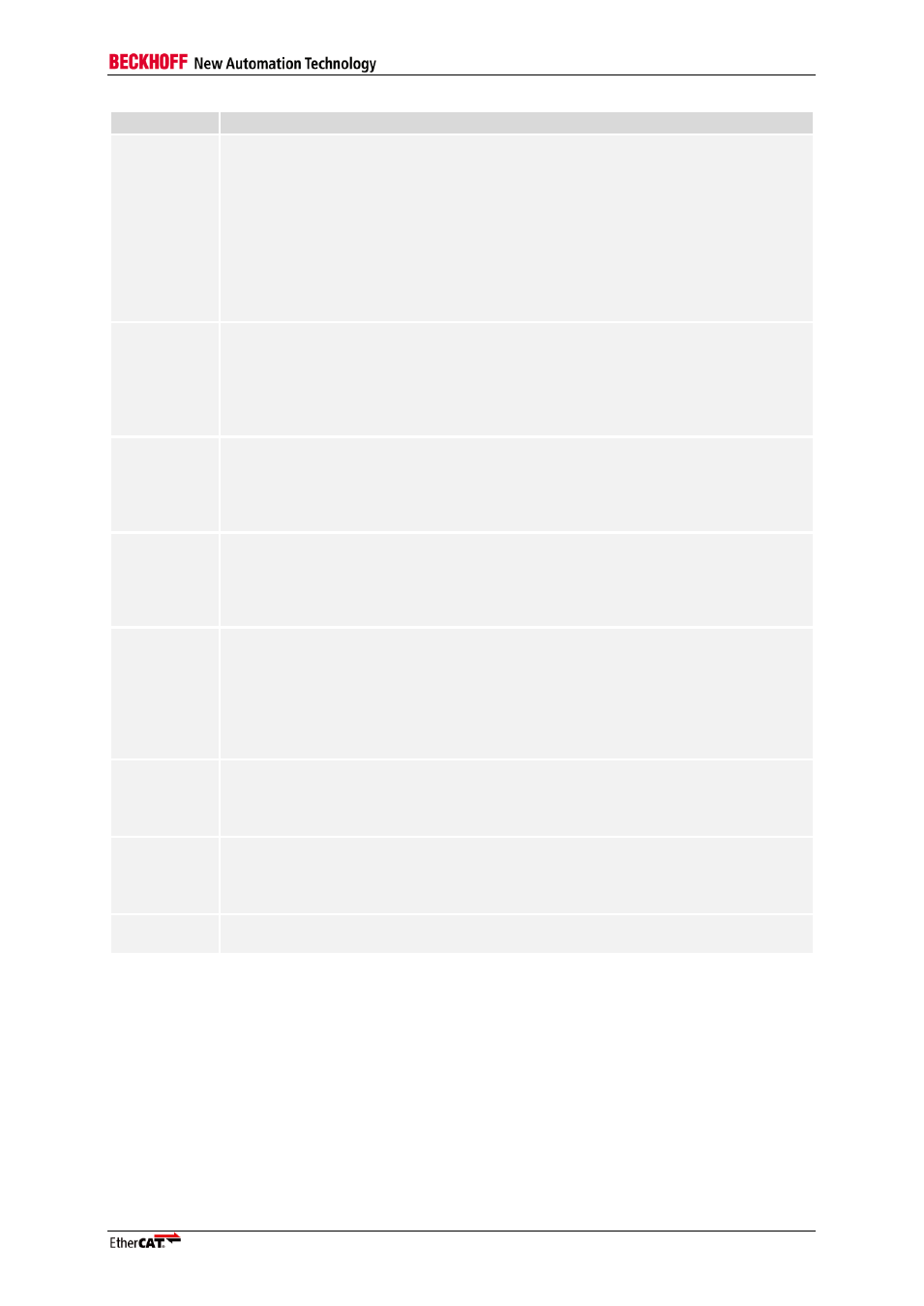

DOCUMENT HISTORY

Slave Controller

– Register Description

II-V

Version

Comment

2.0

DC SYNC Activation register (0x0981.6): bit polarity corrected

Deviation calculation formula for Speed Counter Diff register (0x0932:0x0933)

corrected

AL Event Mask register (0x0204:0x0207): corresponding to AL Event Request

register bits, not to ECAT Event Request register bits

Register availability noted in ESC availability tabs

Register Digital I/O configuration (0x0150): corrected OUTVALID mode = 1

description

Power-on values ET1200 (0x0E00.6): CLK25OUT on PDI[6], not PDI[31]

Editorial changes

2.1

Register bit 0x0220.4 is not available for ESC20

DC System Time (0x0910:0x0917): read value differs between ECAT and PDI

DC Latch Times and DC Event Times are internally latched when lowest byte is

read

DC Speed Counter Start (0x0930:0x0931): minimum value is 0x80

Editorial changes

2.2

ESC20: Register Configured Station Alias (0x0012:0x0013) is taken over after

each EEPROM reload command

MII Management Control register 0x0510[0]: Updated to ET1100-0002

Registers 0x0020 and 0x0030 are readable for ET1100 and ET1200

Editorial changes

2.3

Update to EtherCAT IP Core Release 2.3.0/2.03a (registers 0x0138/0x0139,

0x0150 On-chip Bus, 0x0220, 0x030E, 0x0805 affected)

Separated registers 0x0140 (PDI Control) and 0x0141 (now: ESC

Configuration)

Editorial changes

2.4

ESC DL Control register (0x0100.0): Source MAC address bit is set regardless

of forwarding rule.

Added ESC Feature Bits 0x0008[11:9]

Update to EtherCAT IP Core Release 2.3.2/2.03c

ESC Features 0x0008 and ESC Configuration 0x0141[1]: Enhanced Link

Detection must not be activated for ET1100/ET1200 if EBUS ports are used.

Editorial changes

2.5

Update to EtherCAT IP Core Release 2.4.0/2.04a

ESC20: 0x0140[1:0] and [5:4] are available for SPI PDI

Range for DC Speed Counter Start (0x0930:0x0931) and Speed Counter Diff

(0x0932:0x0933) corrected, representation of Speed Counter Diff mentioned.

2.6

Update to EtherCAT IP Core Release 3.0.0

Added Register DC Receive Time Latch Mode 0x0936

Device Identification in AL Control/Status register 0x0120/0x0130 added

Editorial changes

2.7

Update to EtherCAT IP Core Release 2.4.3/2.04d and 3.0.2/3.00c

Editorial changes