7 sync/latch[1:0] pdi configuration, Sync/latch[1:0] pdi configuration, 0x0151 – BECKHOFF EtherCAT Registers Section II User Manual

Page 48: Sync/latch pdi configuration, R 3.28.7

PDI Configuration (0x0150:0x0153)

II-36

Slave Controller

– Register Description

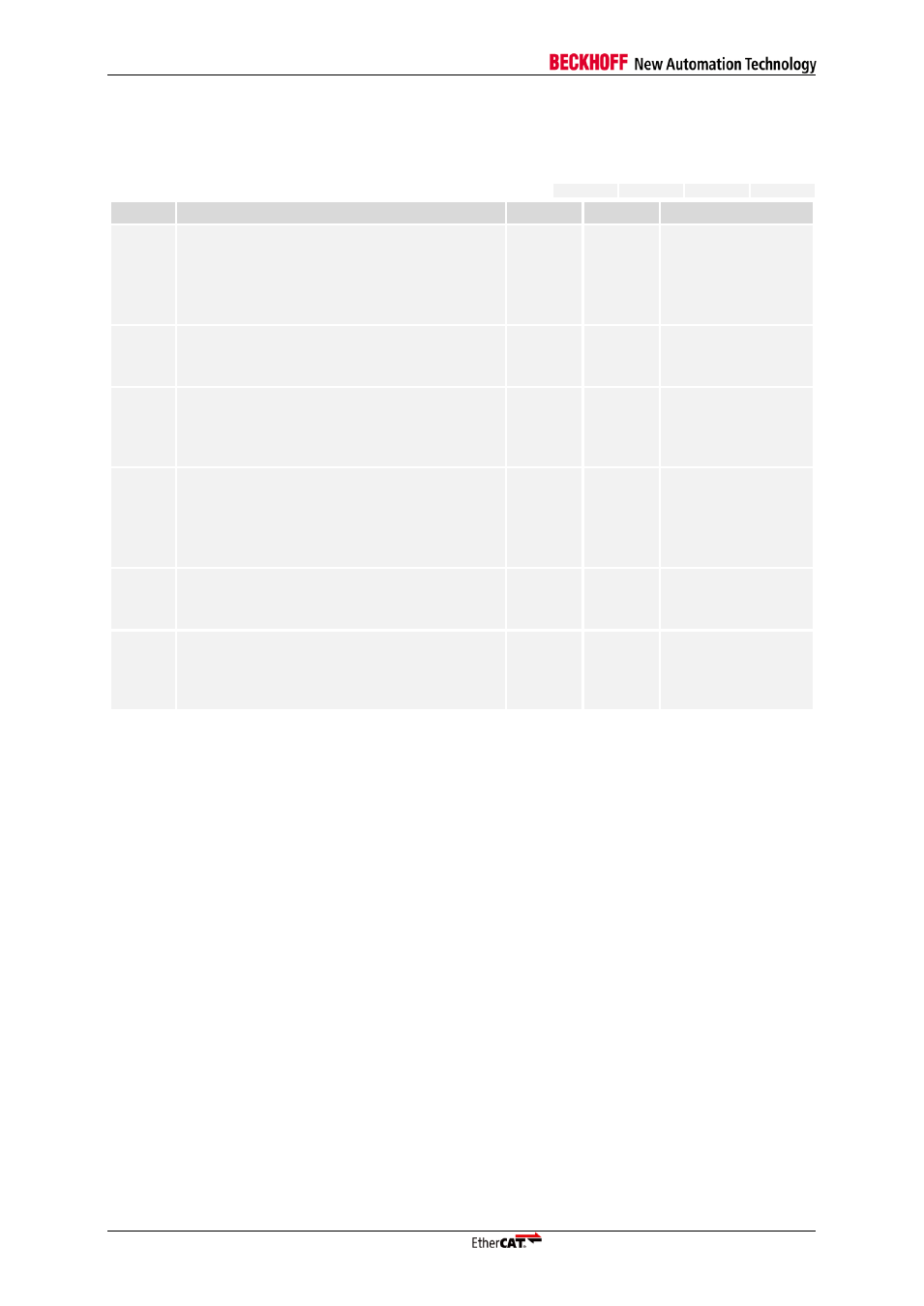

3.28.7 Sync/Latch[1:0] PDI Configuration

Table 45: Register Sync/Latch[1:0] PDI Configuration (0x0151)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

1:0

SYNC0 output driver/polarity:

00: Push-Pull active low

01: Open Drain (active low)

10: Push-Pull active high

11: Open Source (active high)

r/-

r/-

IP Core: 10

Others: 00, later

EEPROM ADR 0x0001

2

SYNC0/LATCH0 configuration*:

0:

LATCH0 Input

1:

SYNC0 Output

r/-

r/-

IP Core: 1

Others: 0, later

EEPROM ADR 0x0001

3

SYNC0 mapped to AL Event Request

register 0x0220.2:

0:

Disabled

1:

Enabled

r/-

r/-

IP Core: Depends on

configuration

Others: 0, later

EEPROM ADR 0x0001

5:4

SYNC1 output driver/polarity:

00: Push-Pull active low

01: Open Drain (active low)

10: Push-Pull active high

11: Open Source (active high)

r/-

r/-

IP Core: 10

Others: 00, later

EEPROM ADR 0x0001

6

SYNC1/LATCH1 configuration*:

0:

LATCH1 input

1:

SYNC1 output

r/-

r/-

IP Core: 1

Others: 0, later

EEPROM ADR 0x0001

7

SYNC1 mapped to AL Event Request

register 0x0220.3:

0:

Disabled

1:

Enabled

r/-

r/-

IP Core: Depends on

configuration

Others: 0, later

EEPROM ADR 0x0001

* The IP Core has concurrent SYNC[1:0] outputs and LATCH[1:0] inputs, independent of this configuration.