15 esc reset ecat (0x0040), 16 esc reset pdi (0x0041), Esc reset ecat (0x0040) – BECKHOFF EtherCAT Registers Section II User Manual

Page 27: Esc reset pdi (0x0041), Table 18: register esc reset ecat (0x0040), Table 19: register esc reset pdi (0x0041), Data link layer, 0x0040, Esc reset, 0x0041

ESC Reset ECAT (0x0040)

Slave Controller

– Register Description

II-15

3.15 ESC Reset ECAT (0x0040)

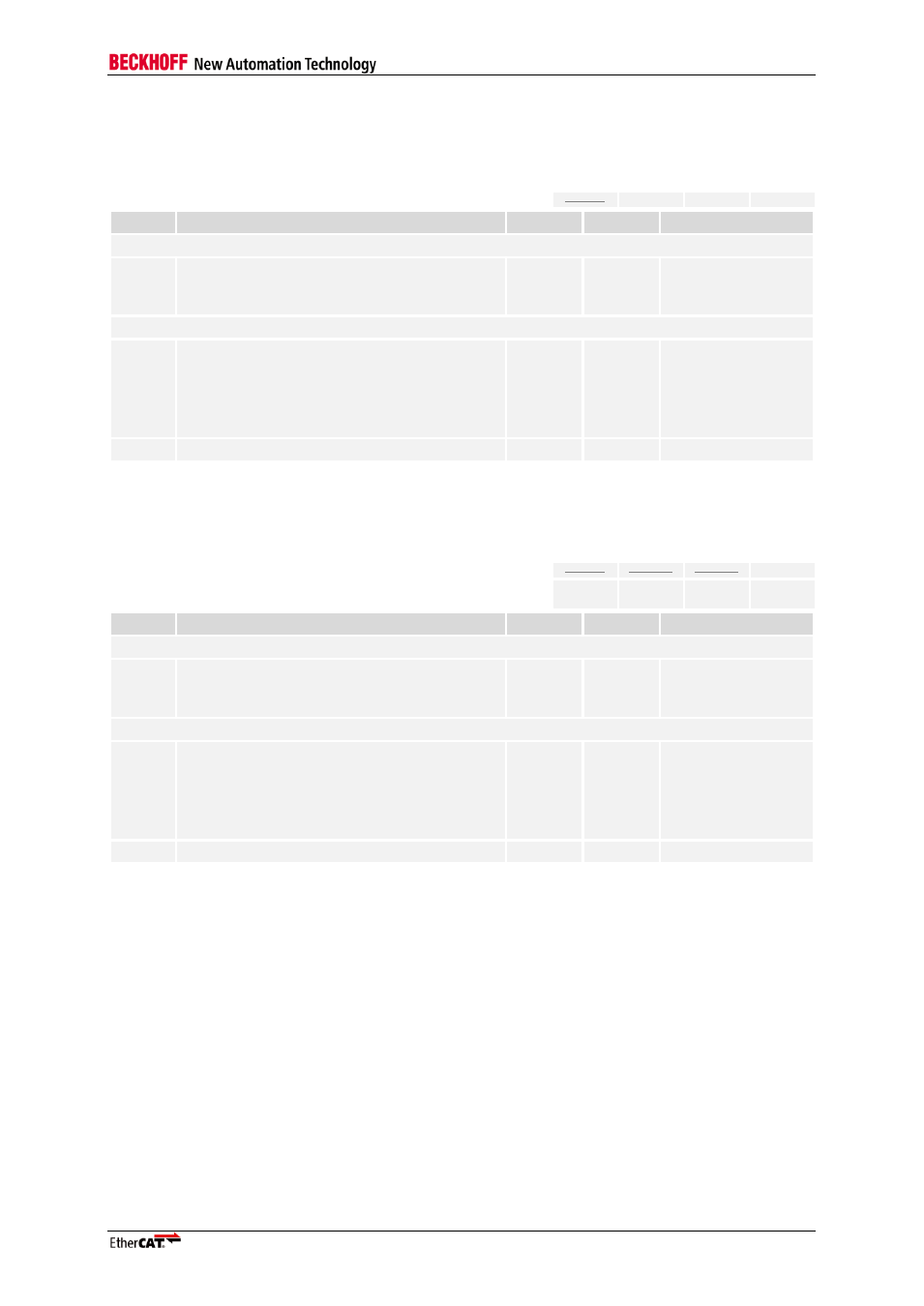

Table 18: Register ESC Reset ECAT (0x0040)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

Write

7:0

A reset is asserted a

fter writing 0x52 (‘R’),

0x45 (‘E’) and 0x53 (‘S’) in this register with 3

consecutive frames.

r/w

r/-

0

Read

1:0

Progress of the reset procedure:

01: after writing 0x52

10: after writing 0x45 (if 0x52 was written

before)

00: else

r/w

r/-

00

7:2

Reserved, write 0

r/-

r/-

0

3.16 ESC Reset PDI (0x0041)

Table 19: Register ESC Reset PDI (0x0041)

ESC20

ET1100

ET1200

IP Core

V2.2.0/

V2.02a

Bit

Description

ECAT

PDI

Reset Value

Write

7:0

A reset is asserted after writing 0x52 (‘R’),

0x45 (‘E’) and 0x53 (‘S’) in this register with 3

consecutive commands.

r/-

r/w

0

Read

1:0

Progress of the reset procedure:

01: after writing 0x52

10: after writing 0x45 (if 0x52 was written

before)

00: else

r/-

r/w

00

7:2

Reserved, write 0

r/-

r/-

0