3 esc availability tab legend, Esc availability tab legend – BECKHOFF EtherCAT Registers Section II User Manual

Page 18

Address Space Overview

II-6

Slave Controller

– Register Description

1.3

ESC Availability Tab Legend

The availability of registers and exceptions for individual register bits or IP Core versions are indicated

in a small area at the top right edge of each register table.

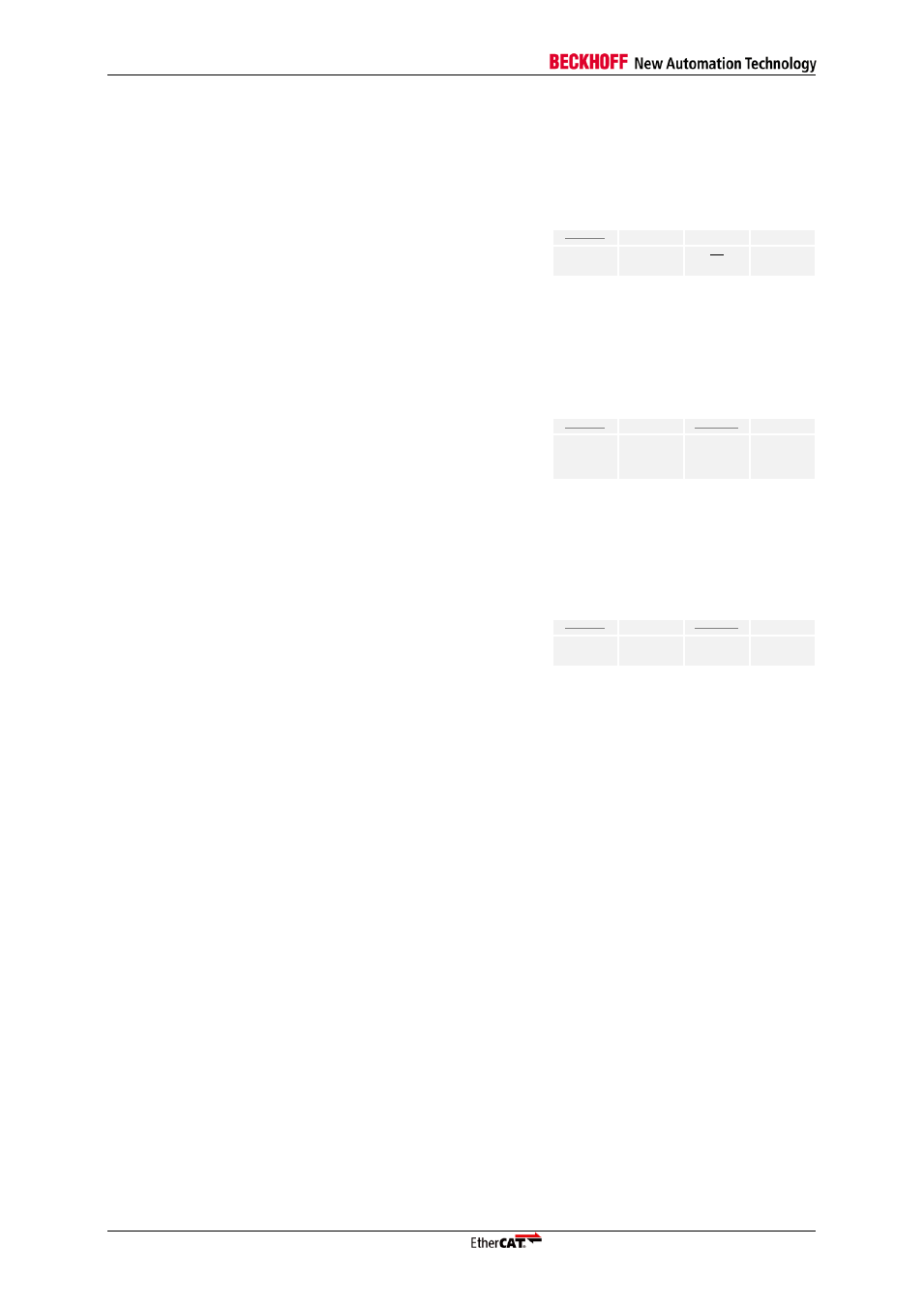

Example 1:

ESC20

ET1100

ET1200

IP Core

[5]

V2.0.0/

V2.00a

Register is not available for ESC20 (reserved)

Register is available for ET1100 (all bits mentioned below)

Register is available for ET1200, except for bit 5 which is reserved

Register is available for IP Core since V2.0.0/V2.00a, reserved for previous versions

Example 2:

ESC20

ET1100

ET1200

IP Core

write

config.

[5]

V2.0.0/

V2.00a

Register is available for ET1100 (read), write access is optionally available (e.g. ESI EEPROM or

IP Core configuration)

Register is available for IP Core, bit 5 is available since V2.0.0/V2.00a, bit 5 is not available for

previous versions (and reserved)

Example 3:

ESC20

ET1100

ET1200

IP Core

[63:16]

config.

V2.0.0/

V2.00a

Register is available for ET1100, bits [63:16] are optionally available (e.g. ESI EEPROM or IP

Core configuration)

Register is optionally available/configurable for IP Core since V2.0.0/V2.00a

(“IP Core” is not

bold)