49 distributed clocks (0x0900:0x09ff), 1 receive times, Distributed clocks (0x0900:0x09ff) – BECKHOFF EtherCAT Registers Section II User Manual

Page 73: Receive times, 0x0900:0x0903, Receive time port 0, 0x0904:0x0907, Receive time port 1, 0x0908:0x090b, Receive time port 2

Distributed Clocks (0x0900:0x09FF)

Slave Controller

– Register Description

II-61

3.49 Distributed Clocks (0x0900:0x09FF)

3.49.1 Receive Times

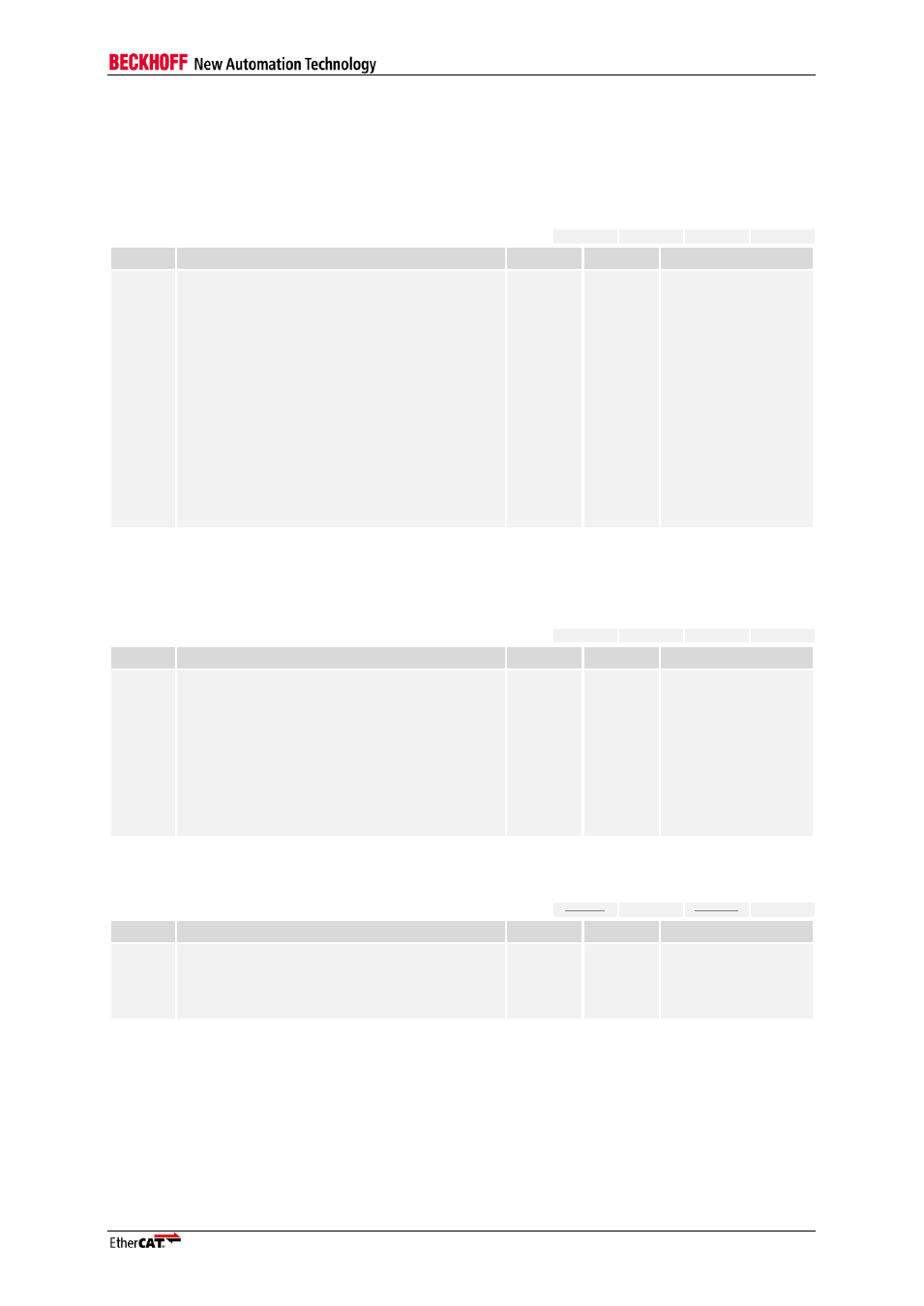

Table 95: Register Receive Time Port 0 (0x0900:0x0903)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

31:0

Write:

A write access to register 0x0900 with

BWR or FPWR latches the local time of

the beginning of the receive frame (start

first bit of preamble) at each port.

Write (ESC20, ET1200 exception):

A write access latches the local time of

the beginning of the receive frame at

port 0. It enables the time stamping at

the other ports.

Read:

Local time of the beginning of the last

receive frame containing a write access

to this register.

r/w

(special

function)

r/-

Undefined

NOTE: The time stamps cannot be read in the same frame in which this register was written.

Table 96: Register Receive Time Port 1 (0x0904:0x0907)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

31:0

Local time of the beginning of a frame (start

first bit of preamble) received at port 1

containing a BWR or FPWR to Register

0x0900.

ESC20, ET1200 exception:

Local time of the beginning of the first frame

received at port 1 after time stamping was

enabled. Time stamping is disabled for this

port afterwards.

r/-

r/-

Undefined

Table 97: Register Receive Time Port 2 (0x0908:0x090B)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

31:0

Local time of the beginning of a frame (start

first bit of preamble) received at port 2

containing a BWR or FPWR to Register

0x0900.

r/-

r/-

Undefined