2 time loop control unit, Time loop control unit, 0x0910:0x0917 – BECKHOFF EtherCAT Registers Section II User Manual

Page 75: System time, 0x0920:0x0927, System time offset, 0x0928:0x092b, System time delay

Distributed Clocks (0x0900:0x09FF)

Slave Controller

– Register Description

II-63

3.49.2 Time Loop Control Unit

Time Loop Control unit is usually assigned to ECAT. Write access to Time Loop Control registers by

PDI (and not ECAT) is only possible with explicit IP Core configuration.

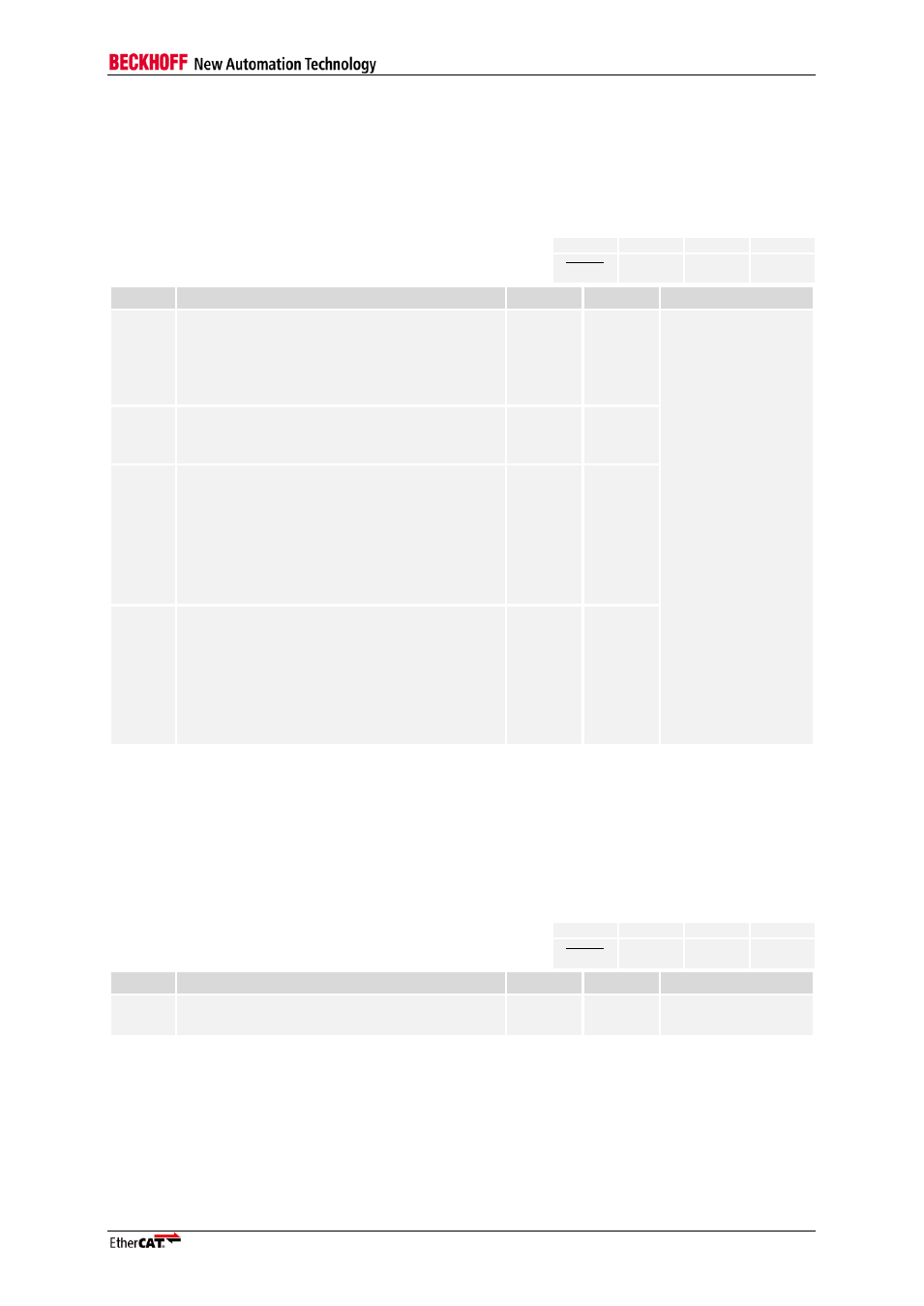

Table 100: Register System Time (0x0910:0x0913 [0x0910:0x0917])

ESC20

ET1100

ET1200

IP Core

[63:32]

[63:32]

config.

Bit

Description

ECAT

PDI

Reset Value

63:0

ECAT read access: Local copy of the System

Time when the frame passed the reference

clock (i.e., including System Time Delay).

Time latched at beginning of the frame

(Ethernet SOF delimiter)

r

-

0

63:0

PDI read access: Local copy of the System

Time. Time latched when reading first byte

(0x0910)

-

r

31:0

Write access: Written value will be compared

with the local copy of the System time. The

result is an input to the time control loop.

NOTE: written value will be compared at the end

of the frame with the latched (SOF) local copy of

the System time if at least the first byte (0x0910)

was written.

(w)

(special

function)

-

31:0

Write access: Written value will be compared

with Latch0 Time Positive Edge time. The

result is an input to the time control loop.

NOTE: written value will be compared at the end

of the access with Latch0 Time Positive Edge

(0x09B0:0x09B3) if at least the last byte (0x0913)

was written.

-

(w)

(special

function)

NOTE: Write access to this register depends upon ESC configuration (typically ECAT, PDI only with explicit ESC

configuration: System Time PDI controlled).

NOTE: Register 0x0918:0x091F is described in the previous chapter.

Table 101: Register System Time Offset (0x0920:0x0923 [0x0920:0x0927])

ESC20

ET1100

ET1200

IP Core

[63:32]

[63:32]

config.

Bit

Description

ECAT

PDI

Reset Value

63:0

Difference between local time and System

Time. Offset is added to the local time.

r/(w)

r/(w)

0

NOTE: Write access to this register depends upon ESC configuration (typically ECAT, PDI only with explicit ESC

configuration: System Time PDI controlled). Reset internal system time difference filter and speed counter filter by

writing Speed Counter Start (0x0930:0x0931) after changing this value.