1 eeprom emulation with ip core, Eeprom emulation with ip core – BECKHOFF EtherCAT Registers Section II User Manual

Page 61

SII EEPROM Interface (0x0500:0x050F)

Slave Controller

– Register Description

II-49

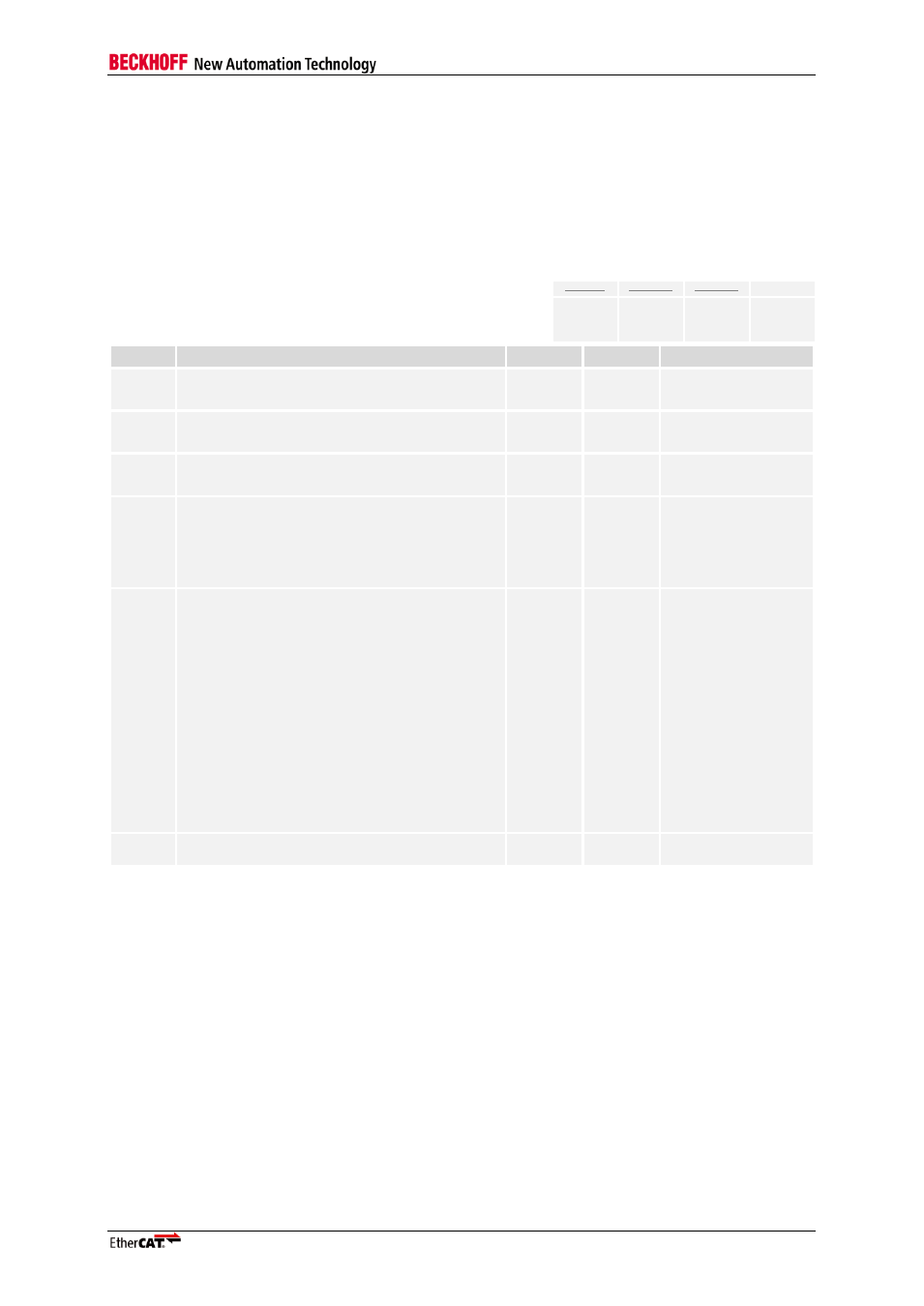

3.45.1 EEPROM emulation with IP Core

Write access to EEPROM Data register 0x0508:0x050F is possible if EEPROM interface is busy

(0x0502.15=1). PDI places EEPROM read data in this register before the pending EEPROM Read

command is acknowledged (writing to 0x0502[10:8]). For Reload command: place the following

information in the EEPROM Data register before acknowledging the command. This data is

automatically transferred to the designated registers when the Reload command is acknowledged:

Table 69: Register EEPROM Data for EEPROM Emulation Reload IP Core (0x0508:0x050F)

ESC20

ET1100

ET1200

IP Core

[27:21]

V2.4.3/

V2.04d

Bit

Description

ECAT

PDI

Reset Value

15:0

Configured Station Alias

(reloaded into 0x0012[15:0])

r/-

r/[w]

0

16

Enhanced Link Detection for all ports

(reloaded into 0x0141[1])

r/-

r/[w]

0

20:17

Enhanced Link Detection for individual ports

(reloaded into 0x0141[7:4])

r/-

r/[w]

0

24:21

ESC DL configuration

(loaded into register 0x0100[23:20])

NOTE: This value is only taken over at the first

EEPROM loading

r/-

r/[w]

0

27:25

FIFO Size reduction (loaded into register

0x0100[18:16]:

000: FIFO Size 7

001: FIFO Size 6

010: FIFO Size 5

011: FIFO Size 4

100: FIFO Size 3

101: FIFO Size 2

110: FIFO Size 1

111: FIFO Size 0

NOTE: This value is only taken over at the first

EEPROM loading

r/-

r/[w]

0

31:28

Reserved, write 0

r/-

r/[w]

0

NOTE: r/[w]: write access for EEPROM emulation if read or reload command is pending.