45 sii eeprom interface (0x0500:0x050f), Sii eeprom interface (0x0500:0x050f), Table 63: sii eeprom interface register overview – BECKHOFF EtherCAT Registers Section II User Manual

Page 58: Table 64: register eeprom configuration (0x0500), I eeprom interface, 0x0500, Eeprom configuration, 0x0501, Eeprom pdi access state

SII EEPROM Interface (0x0500:0x050F)

II-46

Slave Controller

– Register Description

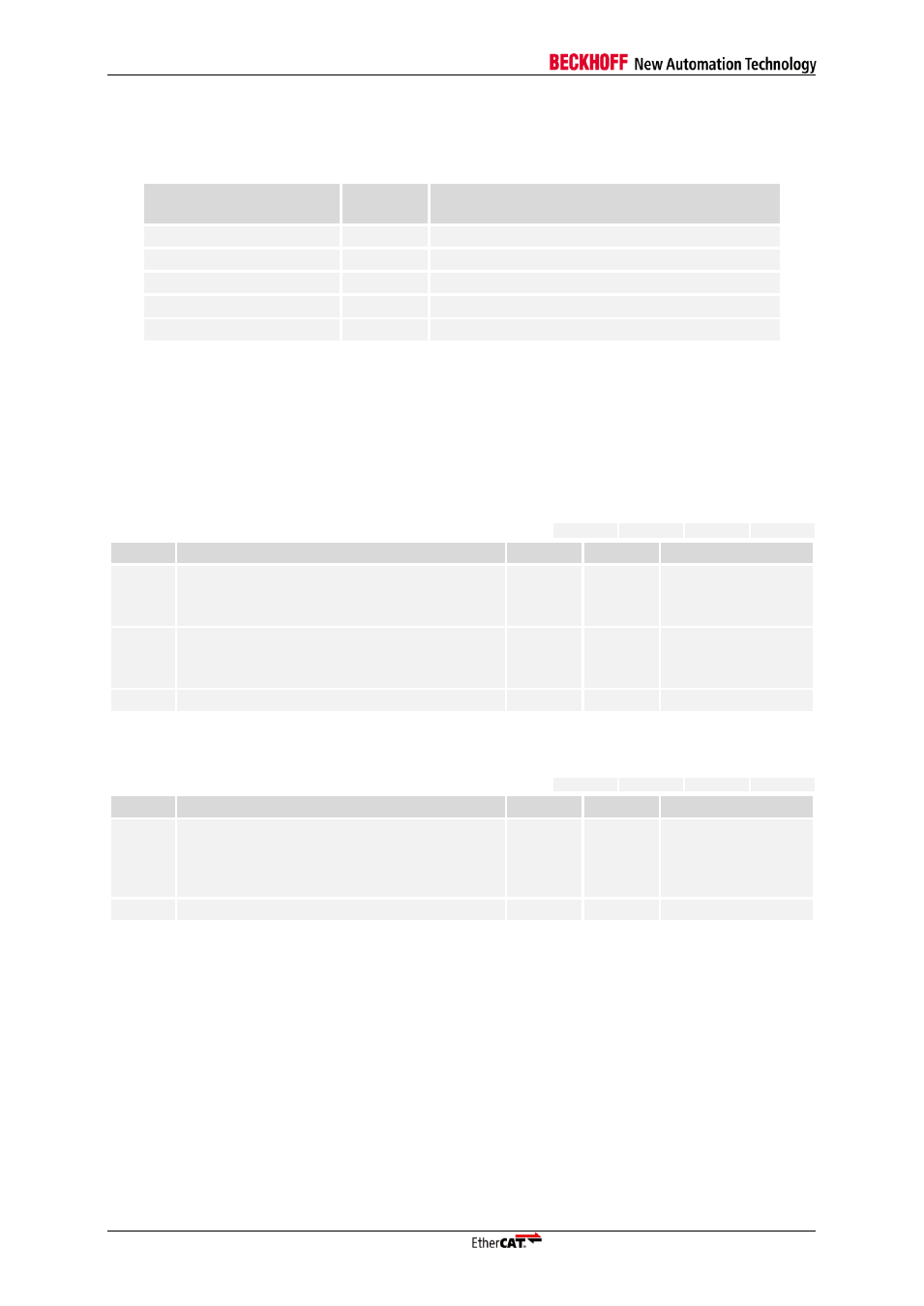

3.45 SII EEPROM Interface (0x0500:0x050F)

Table 63: SII EEPROM Interface Register overview

Register Address

Length

(Byte)

Description

1

1

2

4

4/8

EtherCAT controls the SSI EEPROM interface if EEPROM configuration register 0x0500.0=0 and

EEPROM PDI Access register 0x0501.0=0, otherwise PDI controls the EEPROM interface.

In EEPROM emulation mode, the PDI executes outstanding EEPROM commands. The PDI has

access to some registers while the EEPROM Interface is busy.

Table 64: Register EEPROM Configuration (0x0500)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

0

EEPROM control is offered to PDI:

0:

no

1:

yes (PDI has EEPROM control)

r/w

r/-

0

1

Force ECAT access:

0:

Do not change Bit 501.0

1:

Reset Bit 501.0 to 0

r/w

r/-

0

7:2

Reserved, write 0

r/-

r/-

0

Table 65: Register EEPROM PDI Access State (0x0501)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

0

Access to EEPROM:

0:

PDI releases EEPROM access

1:

PDI takes EEPROM access (PDI has

EEPROM control)

r/-

r/(w)

0

7:1

Reserved, write 0

r/-

r/-

0

NOTE: r/(w): write access is only possible if 0x0500.0=1 and 0x0500.1=0.