0x0935, Speed counter filter depth – BECKHOFF EtherCAT Registers Section II User Manual

Page 77

Distributed Clocks (0x0900:0x09FF)

Slave Controller

– Register Description

II-65

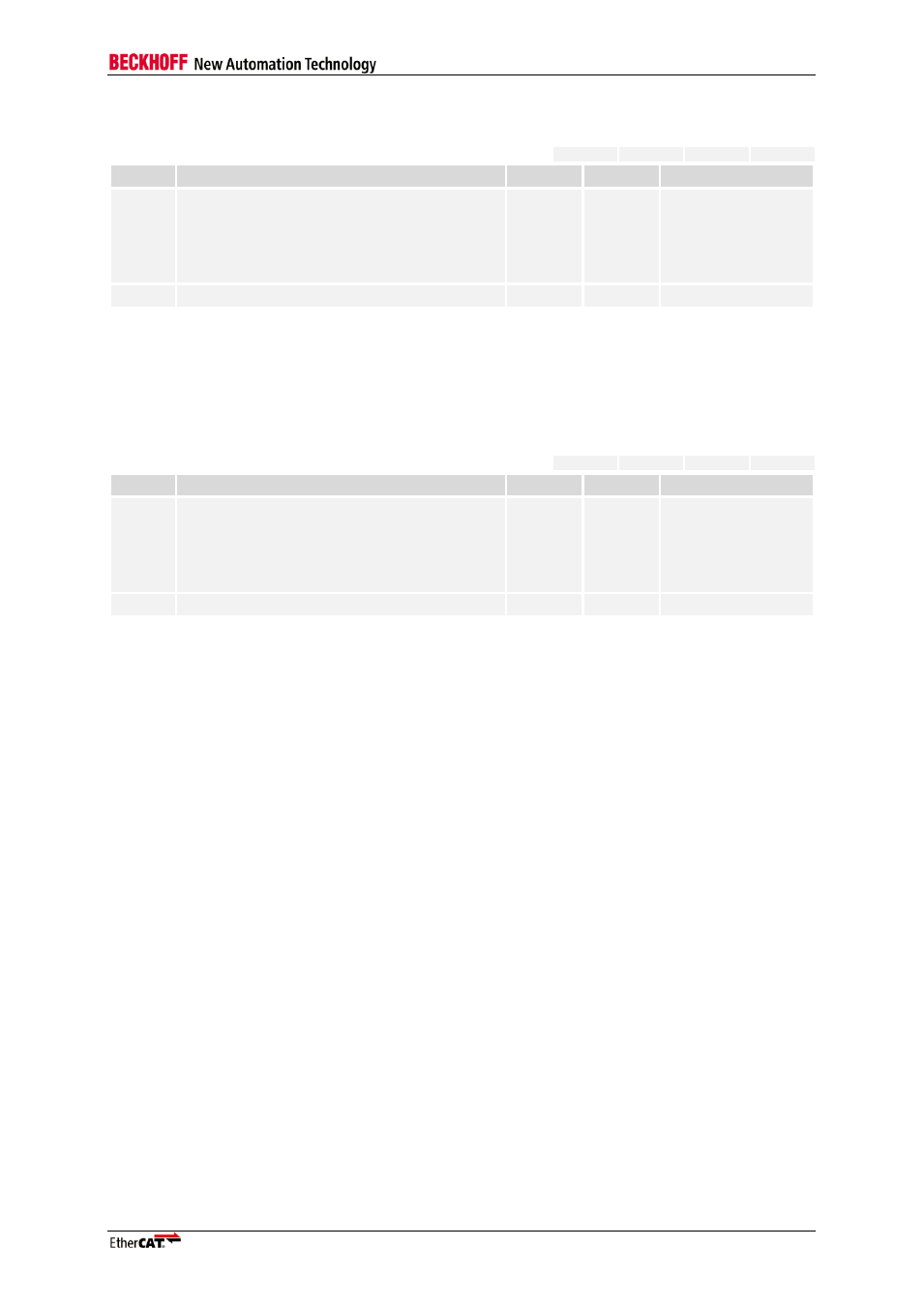

Table 106: Register System Time Difference Filter Depth (0x0934)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

3:0

Filter depth for averaging the received

System Time deviation

IP Core since V2.2.0/V2.02a:

A write access resets System Time

Difference (0x092C:0x092F)

r/(w)

r/(w)

4

7:4

Reserved, write 0

r/-

r/-

0

NOTE: Write access to this register depends upon ESC configuration (typically ECAT, PDI only with explicit ESC

configuration: System Time PDI controlled).

ET1100, ET1200, ESC20, IP Core before V2.2.0/V2.02a: Reset System Time Difference by writing Speed

Counter Start (0x0930:0x0931) after changing this value.

Table 107: Register Speed Counter Filter Depth (0x0935)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

3:0

Filter depth for averaging the clock period

deviation

IP Core since V2.2.0/V2.02a:

A write access resets the internal speed

counter filter.

r/(w)

r/(w)

12

7:4

Reserved, write 0

r/-

r/-

0

NOTE: Write access to this register depends upon ESC configuration (typically ECAT, PDI only with explicit ESC

configuration: System Time PDI controlled) .

ET1100, ET1200, ESC20, IP Core before V2.2.0/V2.02a: Reset internal speed counter filter by writing Speed

Counter Start (0x0930:0x0931) after changing this value.