0x092c:0x092f, System time difference, 0x0930:0x0931 – BECKHOFF EtherCAT Registers Section II User Manual

Page 76: Speed counter start, 0x0932:0x0933, Speed counter diff, 0x0934, System time difference filter depth

Distributed Clocks (0x0900:0x09FF)

II-64

Slave Controller

– Register Description

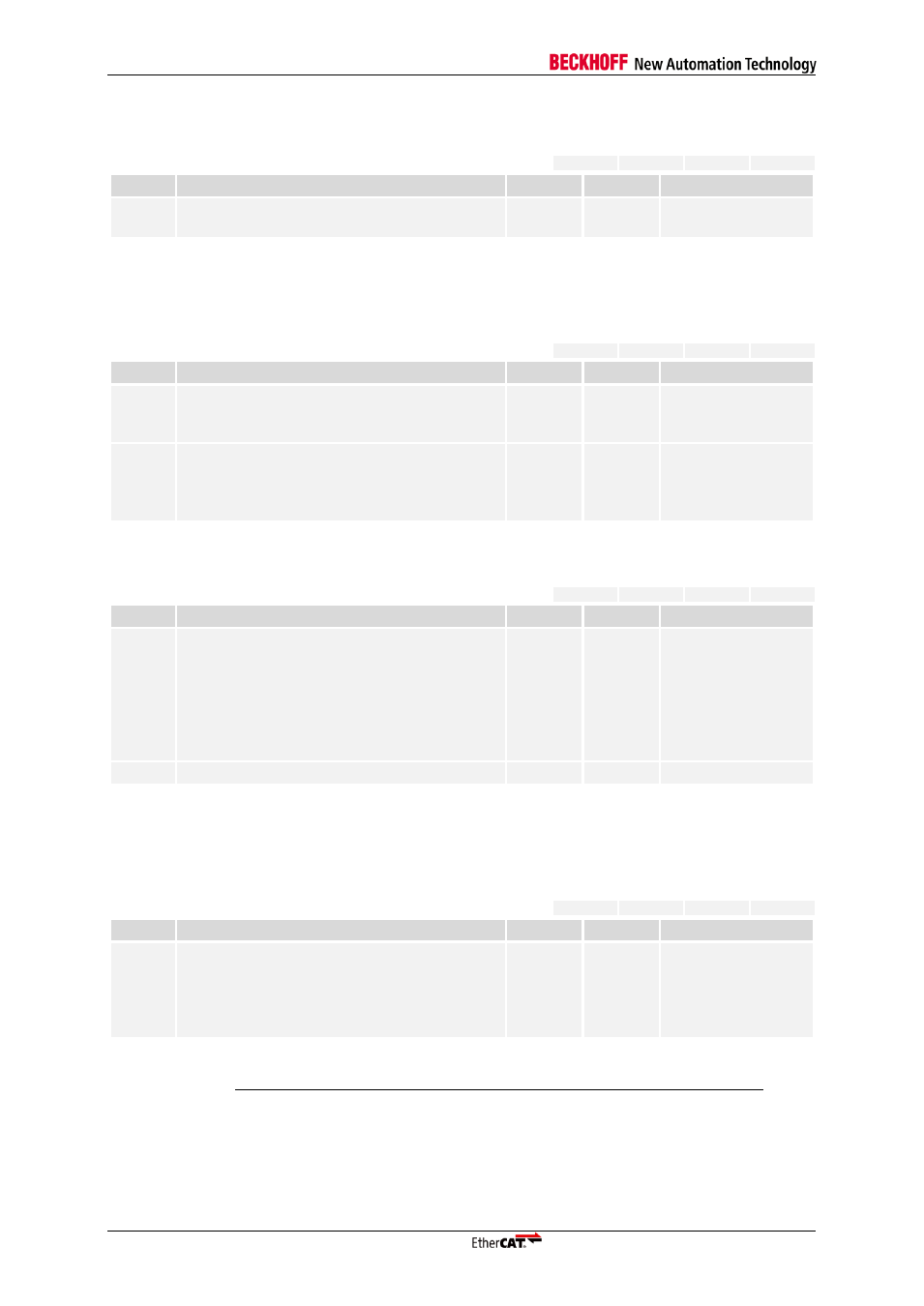

Table 102: Register System Time Delay (0x0928:0x092B)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

31:0

Delay between Reference Clock and the

ESC

r/(w)

r/(w)

0

NOTE: Write access to this register depends upon ESC configuration (typically ECAT, PDI only with explicit ESC

configuration: System Time PDI controlled). Reset internal system time difference filter and speed counter filter by

writing Speed Counter Start (0x0930:0x0931) after changing this value.

Table 103: Register System Time Difference (0x092C:0x092F)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

30:0

Mean difference between local copy of

System Time and received System Time

values

r/-

r/-

0

31

0:

Local copy of System Time greater than

or equal received System Time

1:

Local copy of System Time smaller than

received System Time

r/-

r/-

0

Table 104: Register Speed Counter Start (0x0930:0x931)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

14:0

Bandwidth for adjustment of local copy of

System Time (larger values

→ smaller

bandwidth and smoother adjustment)

A write access resets System Time

Difference (0x092C:0x092F) and Speed

Counter Diff (0x0932:0x0933).

Minimum value: 0x0080 to 0x3FFF

r/(w)

r/(w)

0x1000

15

Reserved, write 0

r/-

r/-

0

NOTE: Write access to this register depends upon ESC configuration (typically ECAT, PDI only with explicit ESC

configuration: System Time PDI controlled).

Table 105: Register Speed Counter Diff (0x0932:0x933)

ESC20

ET1100

ET1200

IP Core

Bit

Description

ECAT

PDI

Reset Value

15:0

Representation of the deviation between

local clock period and Reference Clock’s

clock period

(representation: two’s

complement)

Range: ±(Speed Counter Start

– 0x7F)

r/-

r/-

0x0000

NOTE: Calculate the clock deviation after System Time Difference has settled at a low value as follows:

2)

Diff

Counter

Speed

Start

Counter

2)(Speed

Diff

Counter

Speed

Start

Counter

(Speed

5

Diff

Counter

Speed

Deviation