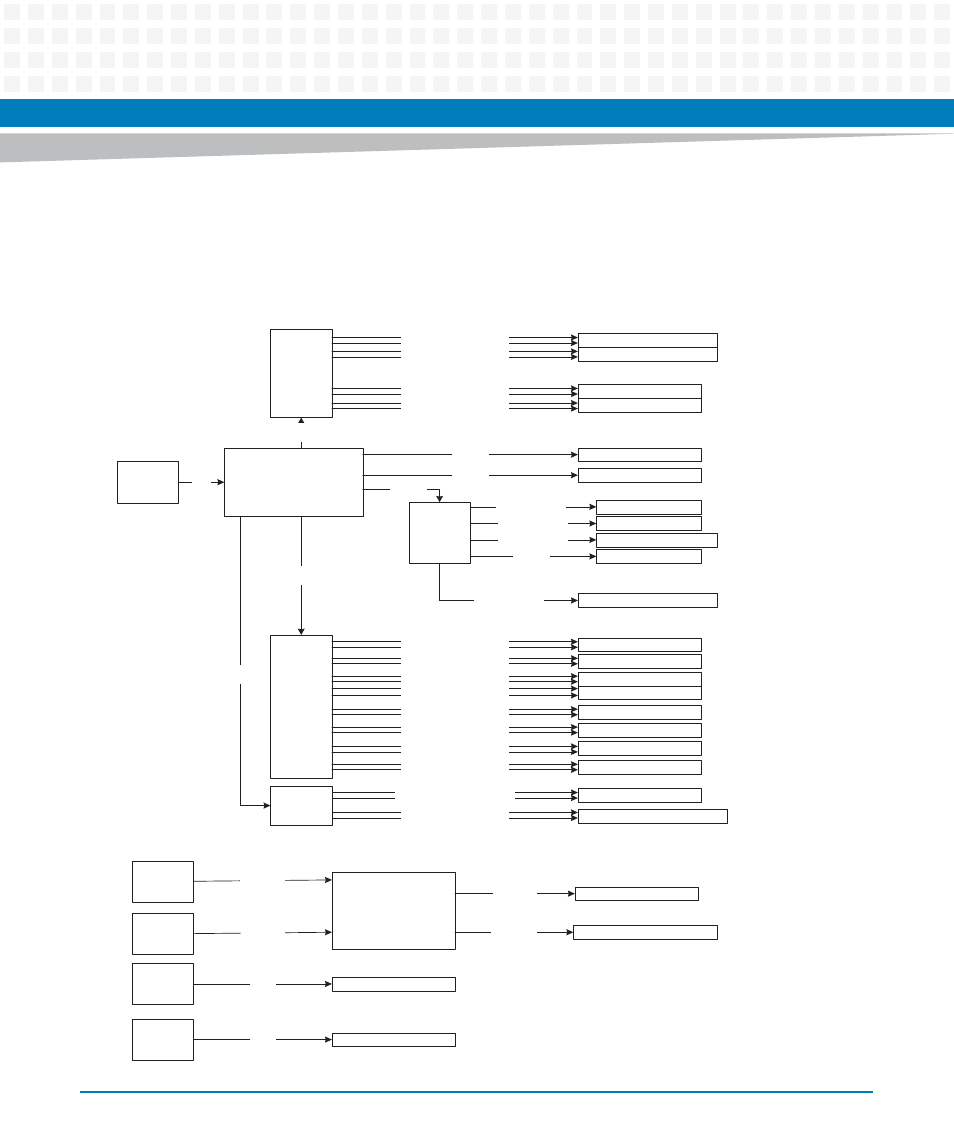

21 clock structure, Figure 4-7, Clock structure – Artesyn MVME8100/MVME8110 Installation and Use (September 2014) User Manual

Page 88: Functional description

Functional Description

MVME8100 / MVME8110 Installation and Use (6806800P25G)

88

4.21 Clock Structure

shows the clock tree implementation for the MVME8100 / MVME8110.

Figure 4-7

Clock Structure

25MHz

XTAL

ICS83905

25Mhz

25Mhz

LVCMOS

25Mhz

LVCMOS

25Mhz

LVCMOS

BCM5482 PHY

BCM54616S PHY

25Mhz

LVCMOS

25Mhz

LVCMOS

ICS9FG104

ICS9FG108

U112

ICS840S07

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

133Mhz LVCMOS

133Mhz LVCMOS

25Mhz

LVCMOS

TSI 148

TSI 384 (VME)

P5020 / P5010 SYSCLK

P5020 / P5010 ETH CTRL1/2

88SE9125 SATA CTRL

32NT24AG2 GCLK0

32NT24AG2 GCLK1

88SE9125 SATA CTRL

1.8432MHz

OSC

CPLD

1.8432MHz

QUART

1.8432MHz

32.768 KHz

P5020 / P5010 RTC

80HCPS1616 SRIO SW

24MHz

OSC

USB2512 HUB

24Mhz

P5020 / P5010 USB

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

P5020 / P5010 SERDES REF1

P5020 / P5010 SERDES REF2

100 Mhz Differential (HCSL)

TSI 384 (VME)

125 Mhz Differential (HCSL)

P5020 / P5010 SERDES REF3

156.25 Mhz Differential (HCSL)

ICS841664

U124

25Mhz

LVCMOS

133Mhz LVCMOS

125Mhz LVCMOS

XMC1

XMC2

TSI 384 (PMC1)

TSI 384 (PMC2)

24MHz

OSC

24Mhz

RTC

32.768 KHz

100 Mhz Differential (HCSL)

100 Mhz Differential (HCSL)

32NT24AG2 PCLK0

32NT24AG2 PCLK2