13 srio ports, Figure 4-3, Pcie ports – Artesyn MVME8100/MVME8110 Installation and Use (September 2014) User Manual

Page 80

Functional Description

MVME8100 / MVME8110 Installation and Use (6806800P25G)

80

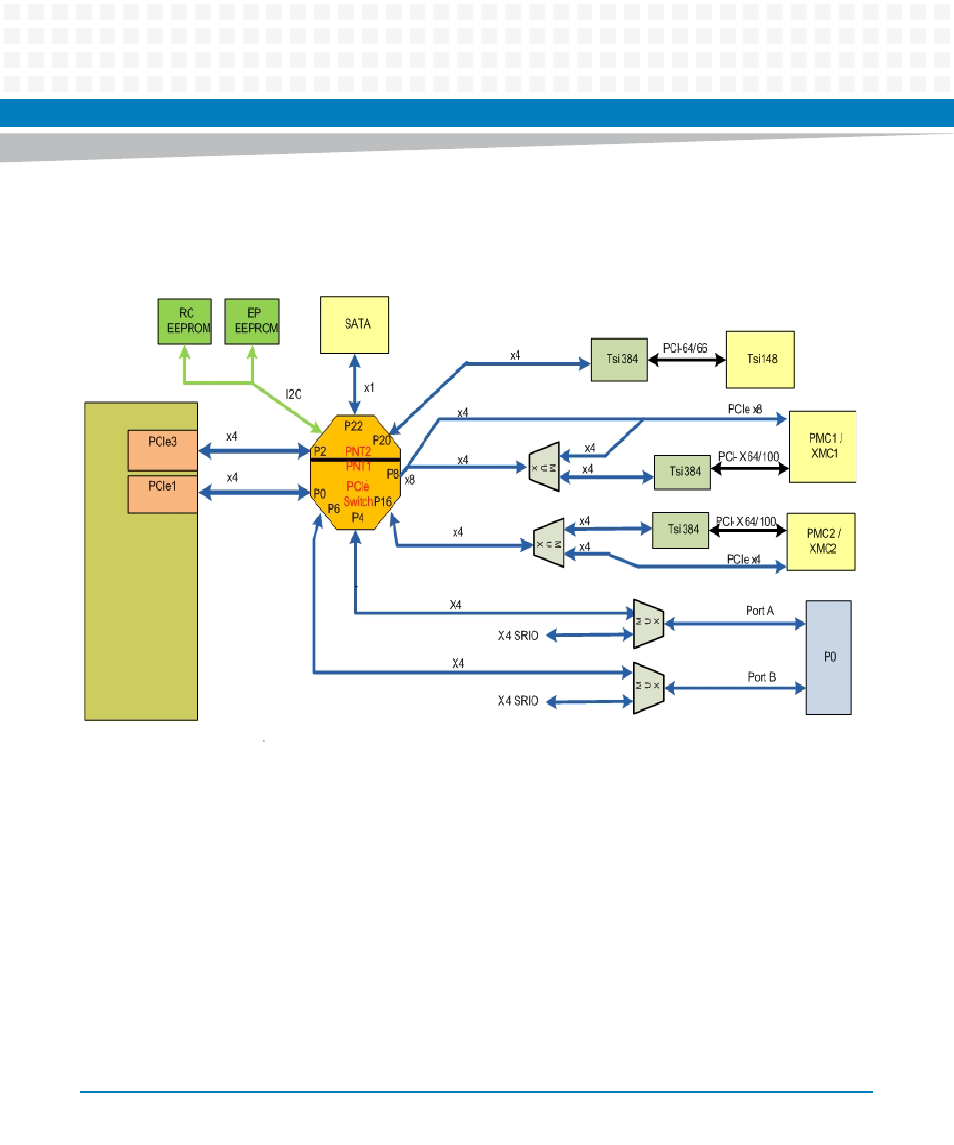

4.13 SRIO Ports

The MVME8100 also provides multiple SRIO ports. The P5020 provides a single x4 SRIO configured for 2.5

GBaud data rate. This port is routed to an IDT 80HCPS1616 SRIO switch for expansion of the SRIO ports. The

SRIO switch supports multiple lane speeds including 1.25, 2.5, 3.125 and 5.0 Gbaud. The MVME8100

provides two x4 SRIO ports which may be routed to the P0 connector through a high speed mux. The

selection of SRIO or PCIe ports to P0 is controlled by the S2-8 configuration switch (see

). The configuration of the SRIO switch ports is controlled by an I2C eeprom connected to the SRIO switch

I2C bus and loaded into the switch following reset. The board provides two separate eeproms so that

separate configuration data can be maintained for the MVME8100 operating as a root complex or as an end

point on the P0 ports. The selection of the root complex or end point eeprom for loading the configuration

data after reset is determined by the root complex configuration switch S4-2 (see

). The

Figure 4-3

PCIe Ports

P5020/P5010