Read-during-write, Byte enable, Byte enable controls – Altera MAX 10 Embedded Memory User Manual

Page 7: Read-during-write -3, Byte enable -3

If you...

...Then

• Activate the read enable during a write

operation, or

• Do not create a read-enable signal

The output port shows:

• the new data being written,

• the old data at that address, or

• a “Don't Care” value when read-during-write

occurs at the same address location.

Read-During-Write

The read-during-write operation occurs when a read operation and a write operation target the same

memory location at the same time.

The read-during-write operation operates in the following ways:

• Same-port

• Mixed-port

Related Information

Customize Read-During-Write Behavior

on page 3-1

Byte Enable

• Memory block that are implemented as RAMs support byte enables.

• The byte enable controls mask the input data, so that only specific bytes of data are written. The

unwritten bytes retain the values written previously.

• The write enable (

wren

) signal, together with the byte enable (

byteena

) signal, control the write

operations on the RAM blocks. By default, the

byteena

signal is high (enabled) and only the

wren

signal controls the writing.

• The byte enable registers do not have a

clear

port.

• M9K blocks support byte enables when the write port has a data width of ×16, ×18, ×32, or ×36 bits.

• Byte enables operate in a one-hot fashion. The LSB of the

byteena

signal corresponds to the LSB of the

data bus. For example, if

byteena = 01

and you are using a RAM block in ×18 mode,

data[8:0]

is

enabled and

data[17:9]

is disabled. Similarly, if

byteena = 11

, both

data[8:0]

and

data[17:9]

are

enabled.

• Byte enables are active high.

Byte Enable Controls

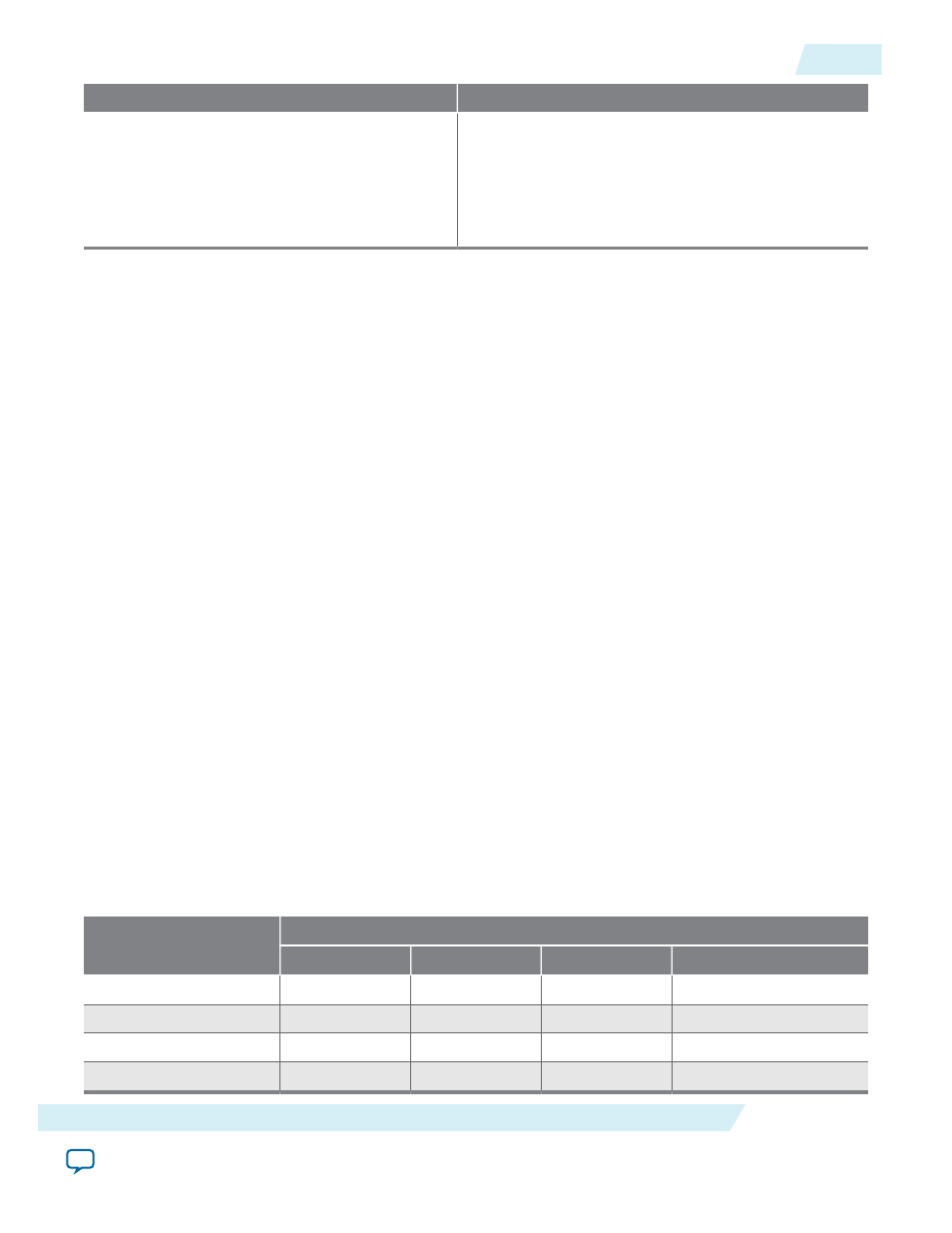

Table 2-1: M9K Blocks Byte Enable Selections

byteena[3:0]

Affected Bytes. Any Combination of Byte Enables is Possible.

datain x 16

datain x 18

datain x 32

datain x 36

[0] = 1

[7:0]

[8:0]

[7:0]

[8:0]

[1] = 1

[15:8]

[17:9]

[15:8]

[17:9]

[2] = 1

—

—

[23:16]

[26:18]

[3] = 1

—

—

[31:24]

[35:27]

UG-M10MEMORY

2015.05.04

Read-During-Write

2-3

MAX 10 Embedded Memory Architecture and Features

Altera Corporation