Altera MAX 10 Embedded Memory User Manual

Page 35

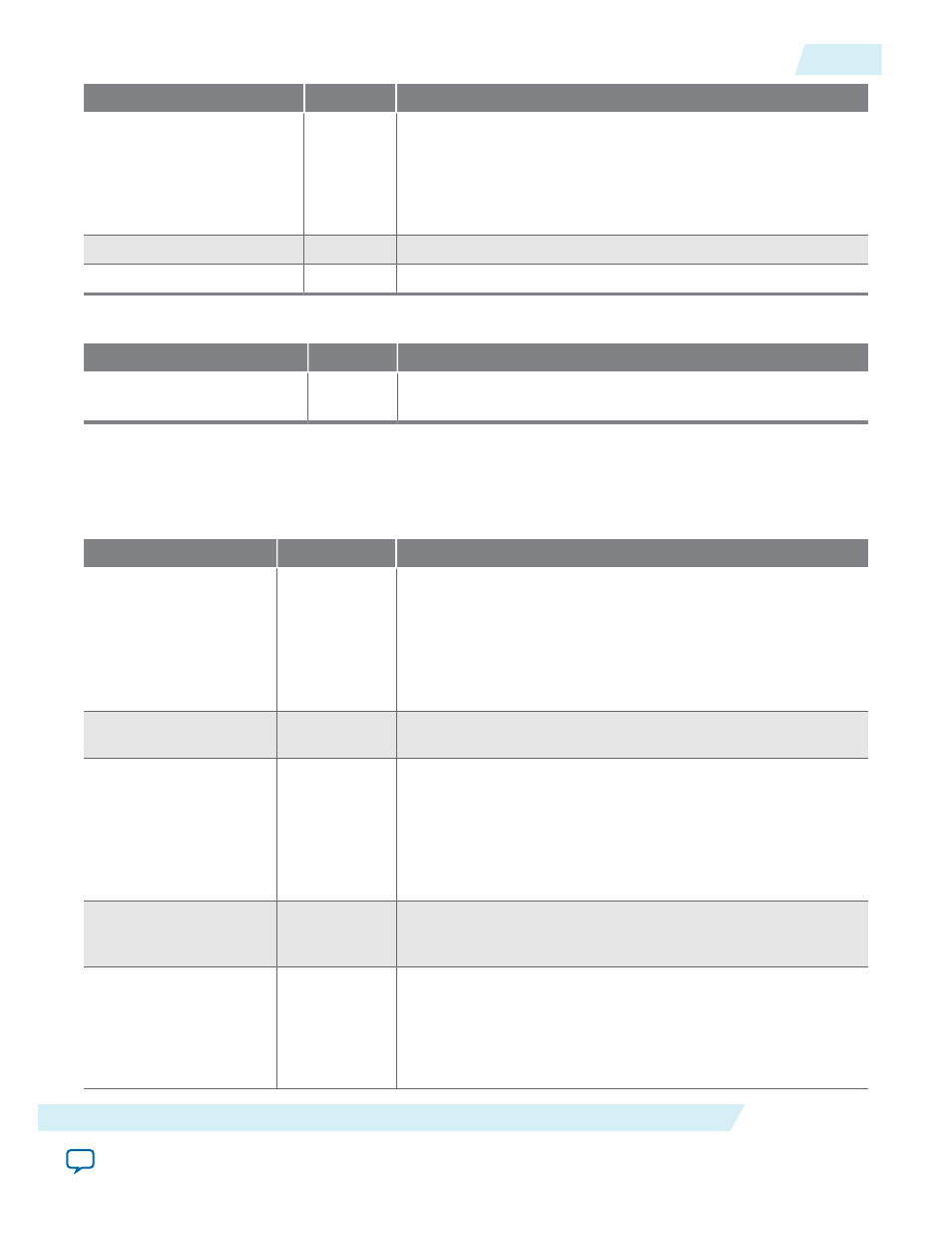

Signal

Required

Description

byteena_a

Optional Byte enable input to mask the

data_a

port so that only specific

bytes, nibbles, or bits of the data are written. The byteena_a

port is not supported in the following conditions:

• If the

implement_in_les

parameter is set to

ON

.

• If the

operation_mode

parameter is set to

ROM

.

outclocken

Optional Clock enable input for

outclock

port.

inclocken

Optional Clock enable input for

inclock

port.

Table 5-2: RAM: 2-Ports IP Core Output Signals (Simple Dual-Port RAM)

Signal

Required

Description

q

Yes

Data output from the memory. The

q

port is required, and

must be equal to the width data port.

RAM: 2-Port IP Core Signals (True Dual-Port RAM) for MAX 10 Devices

Table 5-3: RAM: 2-Port IP Core Input Signals (True Dual-Port RAM)

Signal

Required

Description

data_a

Optional

Data input to port A of the memory. The

data_a

port is

required if the

operation_mode

parameter is set to any of the

following values:

•

SINGLE_PORT

•

DUAL_PORT

•

BIDIR_DUAL_PORT

address_a

Yes

Address input to port A of the memory. The

address_a

port is

required for all operation modes.

wren_a

Optional

Write enable input for

address_a

port. The

wren_a

port is

required if you set the

operation_mode

parameter to any of the

following values:

•

SINGLE_PORT

•

DUAL_PORT

•

BIDIR_DUAL_PORT

data_b

Optional

Data input to port B of the memory. The

data_b

port is

required if the

operation_mode

parameter is set to

BIDIR_

DUAL_PORT

.

address_b

Optional

Address input to port B of the memory. The

address_b

port is

required if the

operation_mode

parameter is set to the

following values:

•

DUAL_PORT

•

BIDIR_DUAL_PORT

UG-M10MEMORY

2015.05.04

RAM: 2-Port IP Core Signals (True Dual-Port RAM) for MAX 10 Devices

5-7

RAM: 2-PORT IP Core References

Altera Corporation