Output read data in simultaneous read and write, Independent clock enables in clock modes, Max 10 embedded memory configurations – Altera MAX 10 Embedded Memory User Manual

Page 14: Port width configurations, Independent clock enables in clock modes -10, Max 10 embedded memory configurations -10, Port width configurations -10

Output Read Data in Simultaneous Read and Write

If you perform a simultaneous read/write to the same address location using the read or write clock mode,

the output read data is unknown. If you want the output read data to be a known value, use single-clock

or input/output clock mode and then select the appropriate read-during-write behavior in the RAM: 1-

PORT and RAM: 2-PORT IP cores.

Related Information

MAX 10 Embedded Memory Clock Modes

on page 2-9

Independent Clock Enables in Clock Modes

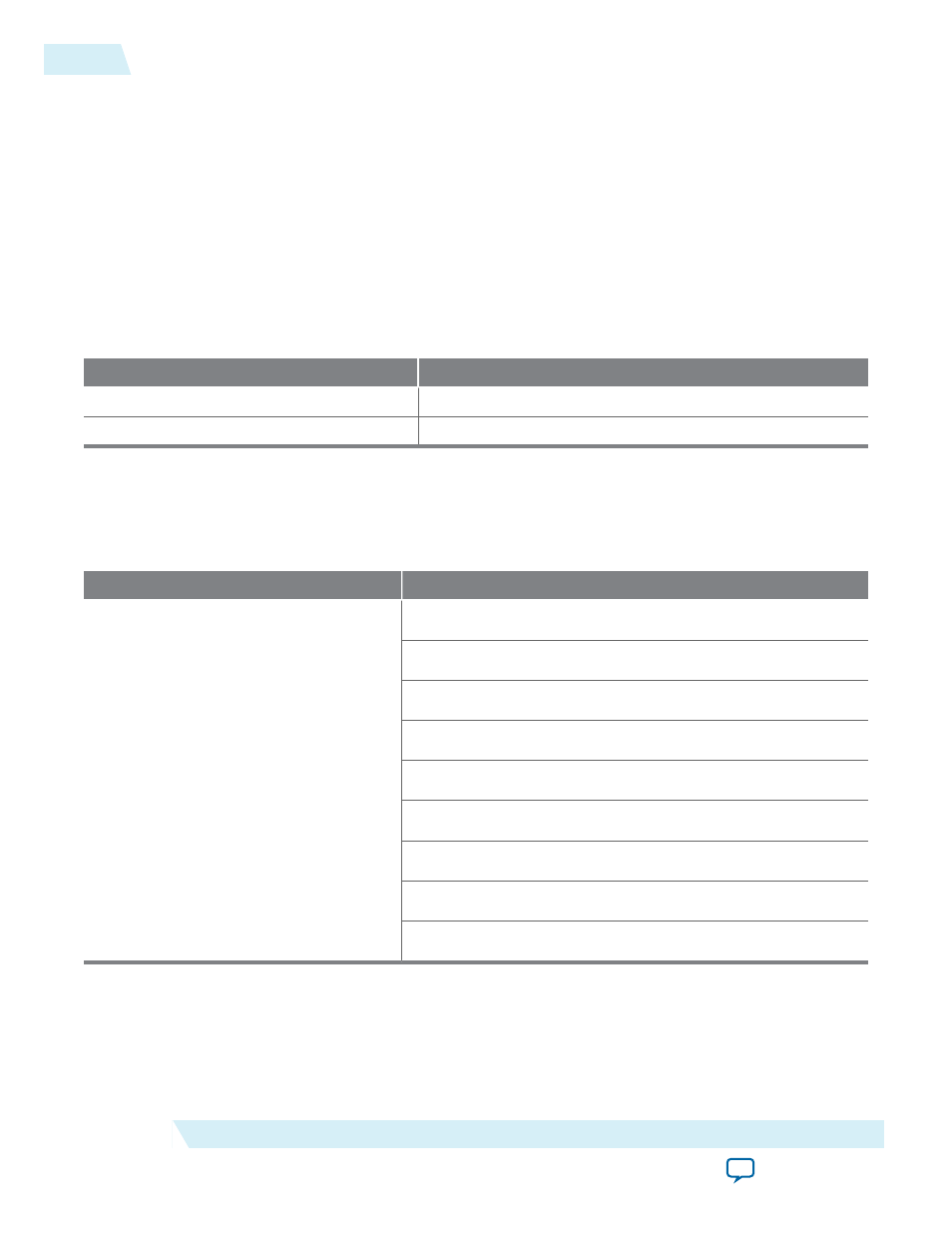

Table 2-3: Supported Clock Modes for Independent Clock Enables

Clock Mode

Description

Read/write

Supported for both the read and write clocks.

Independent

Supported for the registers of both ports.

MAX 10 Embedded Memory Configurations

Table 2-4: Maximum Configurations Supported for M9K Embedded Memory Blocks

Feature

M9K Block

Configurations (depth × width)

8192 × 1

4096 × 2

2048 × 4

1024 × 8

1024 × 9

512 × 16

512 × 18

256 × 32

256 × 36

Port Width Configurations

The following equation defines the port width configuration: Memory depth (number of words) × Width

of the data input bus.

2-10

Output Read Data in Simultaneous Read and Write

UG-M10MEMORY

2015.05.04

Altera Corporation

MAX 10 Embedded Memory Architecture and Features