Parity bit, Read enable, Parity bit -2 – Altera MAX 10 Embedded Memory User Manual

Page 6: Read enable -2

The

rden

and

wren

control signals control the read and write operations for each port of the M9K

memory blocks. You can disable the

rden

or

wren

signals independently to save power whenever the

operation is not required.

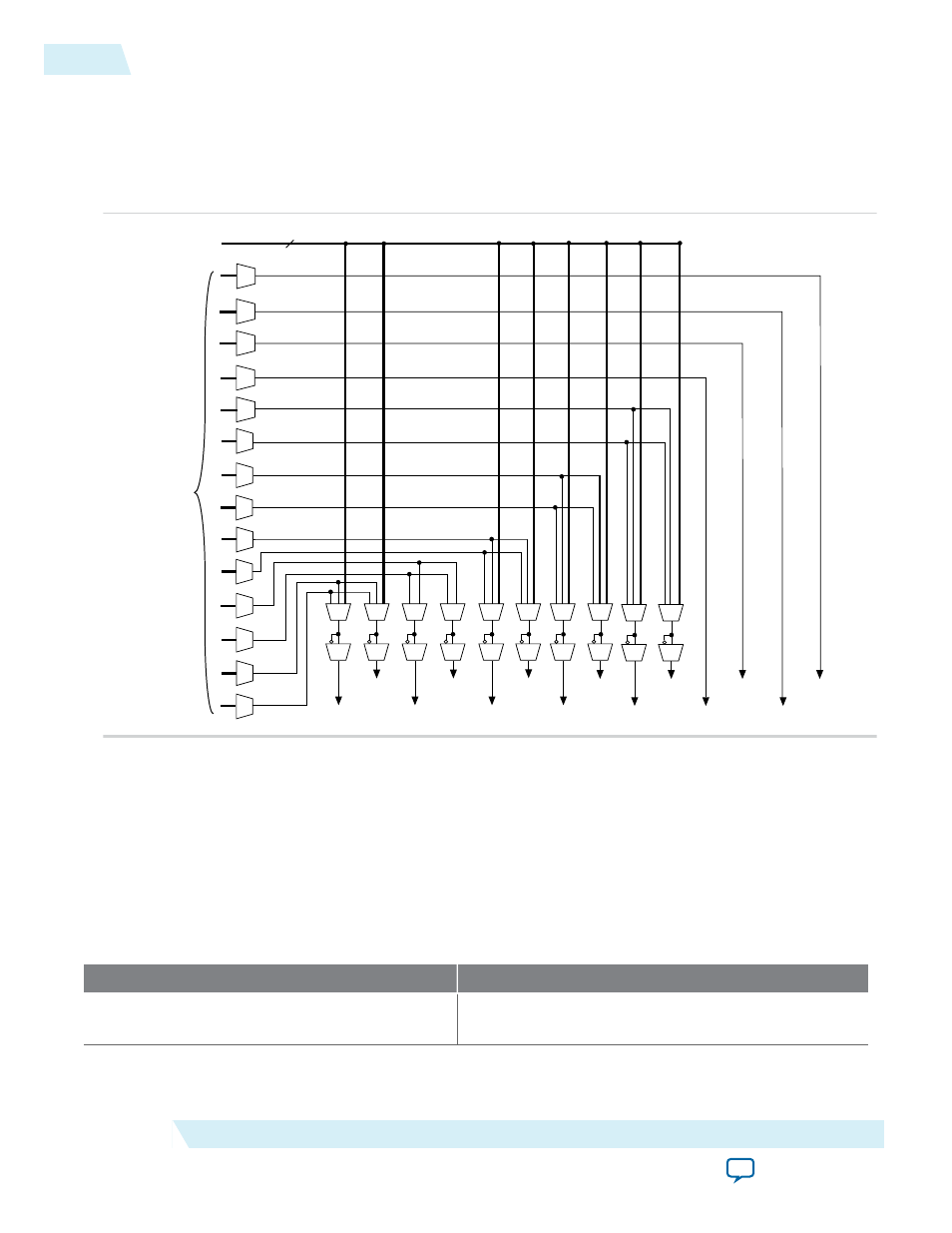

Figure 2-1: Register Clock, Clear, and Control Signals Implementation in M9K Embedded Memory

Block

clock_b

clocken_a

clock_a

clocken_b

aclr_b

aclr_a

Dedicated

Row LAB

Clocks

rden_b

rden_a

6

Local

Interconnect

byteena_b

byteena_a

addressstall_b

addressstall_a

wren_a

wren_b

Parity Bit

You can perform parity checking for error detection with the parity bit along with internal logic

resources. The M9K memory blocks support a parity bit for each storage byte. You can use this bit as

either a parity bit or as an additional data bit. No parity function is actually performed on this bit. If error

detection is not desired, you can use the parity bit as an additional data bit.

Read Enable

M9K memory blocks support the read enable feature for all memory modes.

If you...

...Then

Create the read-enable port and perform a write

operation with the read enable port deasserted

The data output port retains the previous values that

are held during the most recent active read enable.

2-2

Parity Bit

UG-M10MEMORY

2015.05.04

Altera Corporation

MAX 10 Embedded Memory Architecture and Features