Altera MAX 10 Embedded Memory User Manual

Page 48

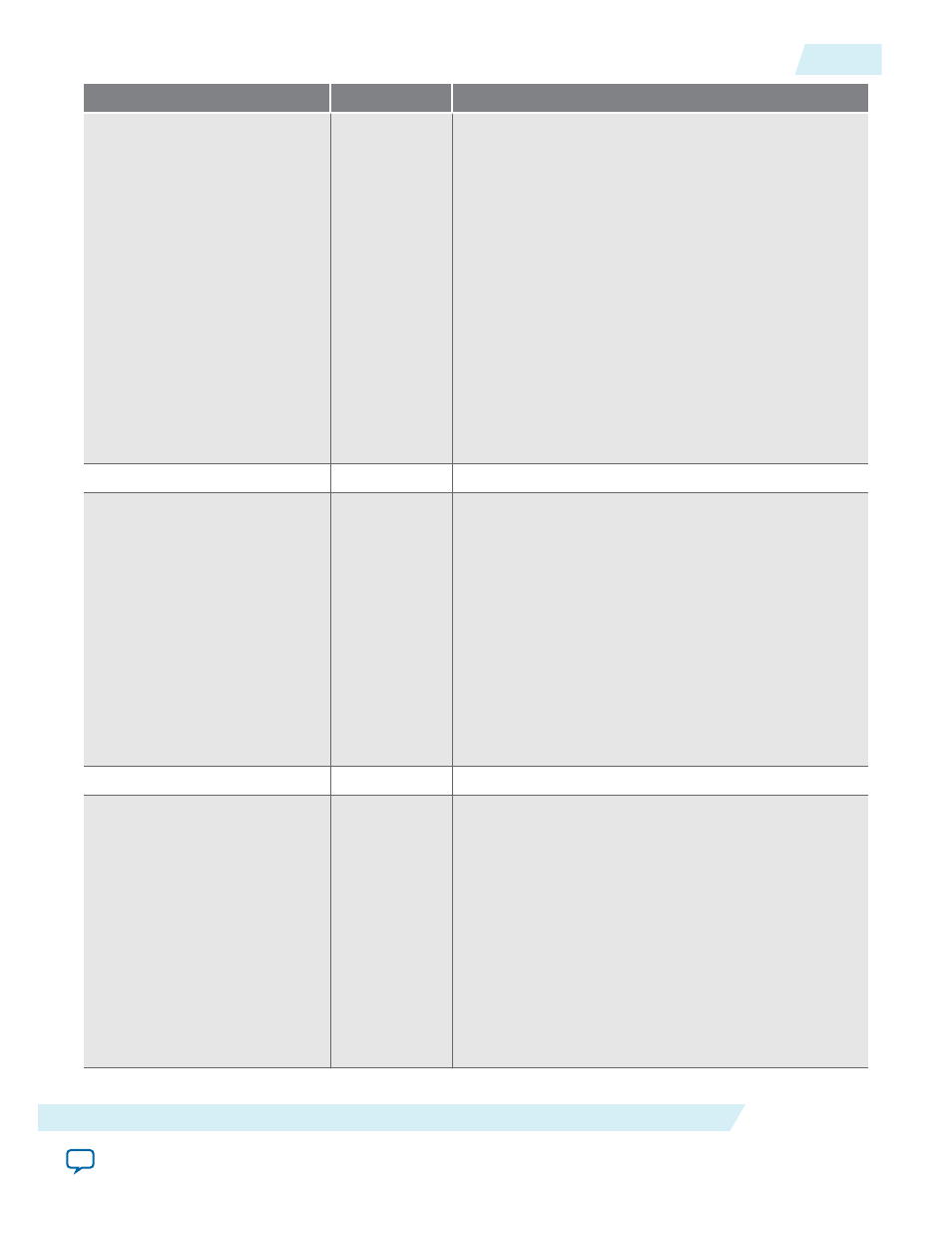

Signal

Required

Description

clock

Yes

The following list describes which of your memory

clock must be connected to the

clock

port, and port

synchronization in different clock modes:

• Single clock—Connect your single source clock to

clock

port. All registered ports are synchronized by

the same source clock.

• Read/Write—Connect your write clock to

clock

port. All registered ports related to write operation,

such as

data_a

port,

address_a

port,

wren_a

port,

and

byteena_a

port are synchronized by the write

clock.

• Input/Output—Connect your input clock to

clock

port. All registered input ports are synchronized by

the input clock.

• Independent clock—Connect your port A clock to

clock

port. All registered input and output ports of

port A are synchronized by the port A clock.

clken

Optional

Clock enable input for

clock

port.

inclock

Yes

The following list describes which of your memory

clock must be connected to the

inclock

port, and port

synchronization in different clock modes:

• Single clock—Connect your single source clock to

inclock

port and

outclock

port. All registered

ports are synchronized by the same source clock.

• Read/Write—Connect your write clock to

inclock

port. All registered ports related to write operation,

such as

data

port,

wraddress

port,

wren

port, and

byteena

port are synchronized by the write clock.

• Input/Output—Connect your input clock to

inclock

port. All registered input ports are

synchronized by the input clock.

inclocken

Optional

Clock enable input for

inclock

port.

outclock

Yes

The following list describes which of your memory

clock must be connected to the

outclock

port, and

port synchronization in different clock modes:

• Single clock—Connect your single source clock to

inclock

port and

outclock

port. All registered

ports are synchronized by the same source clock.

• Read/Write—Connect your read clock to

outclock

port. All registered ports related to read operation,

such as

rdaddress

port,

rdren

port, and

q

port are

synchronized by the read clock.

• Input/Output—Connect your output clock to

outclock

port. The registered

q

port is synchron‐

ized by the output clock.

UG-M10MEMORY

2015.05.04

ROM: 1-PORT IP Core Signals For MAX 10 Devices

6-3

ROM: 1-PORT IP Core References

Altera Corporation